A kind of strained channel transistor and its preparation method

A strained channel and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing device performance, affecting channel carrier mobility, affecting device performance, etc. Carrier mobility, improvement of hot carrier effect, and effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

[0053] like Figures 1 to 8 As shown, a preparation method of a strained channel transistor in the present application includes the following steps:

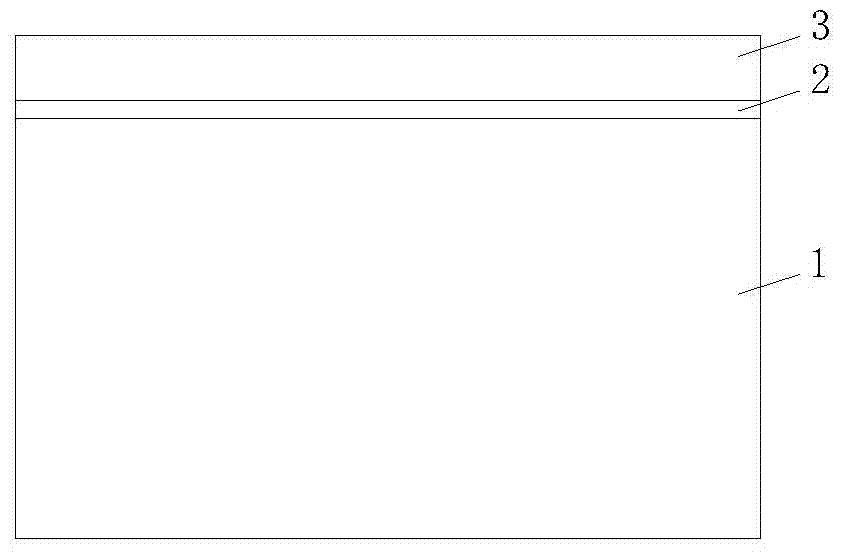

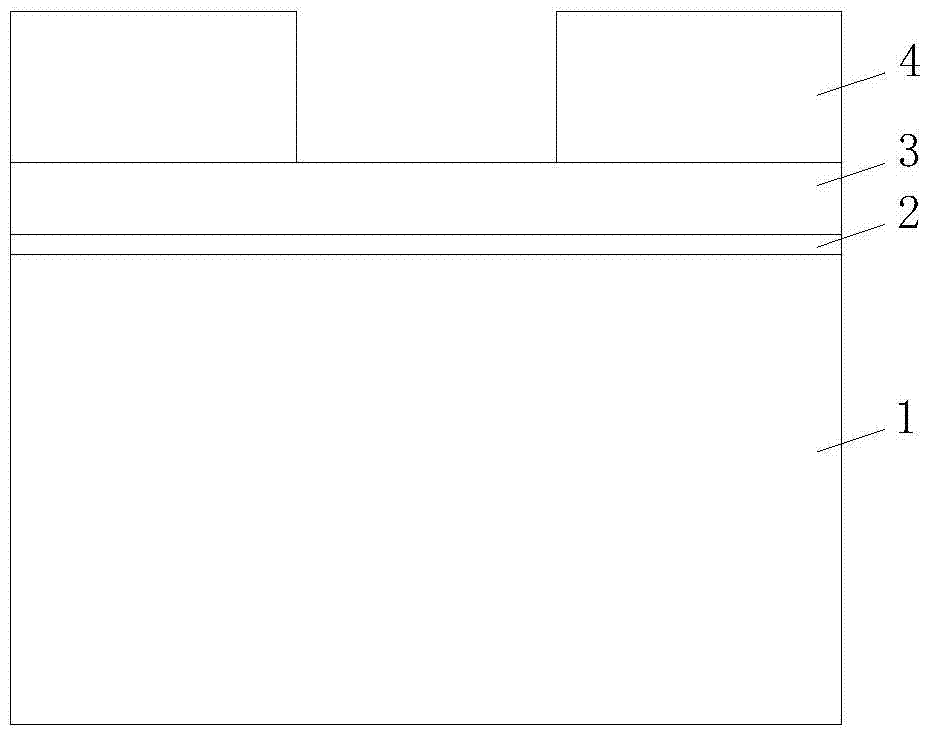

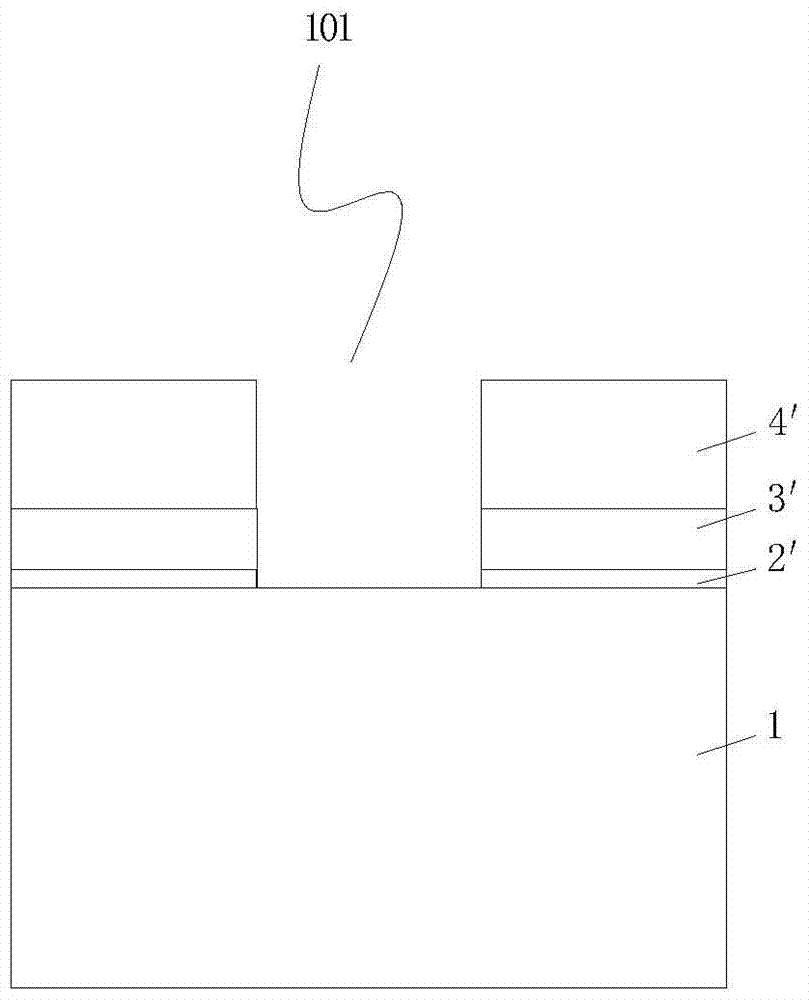

[0054] Step S1: Provide an SOI (Silicon On Insulator, silicon on insulator) structure, which includes a substrate 1, a buried oxide layer 2, and a silicide layer 3 from bottom to top; preferably, the substrate 1 is germanium (Ge) The substrate, the material of the silicide layer 3 is silicon nitride (SiC), and the thickness of the silicide layer 3 is 20-50 nm, such as figure 1 structure shown. In the embodiment of the present invention, whether to pre-dope the source and drain of the silicide layer 3 is selected according to the process requirements, and specific related descriptions can be found below;

[0055] Deposit a mask layer 4 to cover the upper surface of the silicide layer 3, perform a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More