VDMOS device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing manufacturing cost and increasing process difficulty, so as to improve performance, reduce source contact resistance, increase The effect of contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

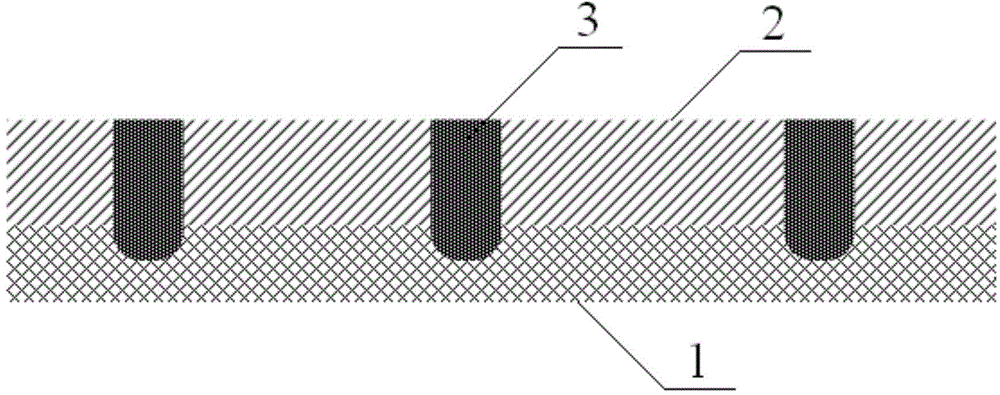

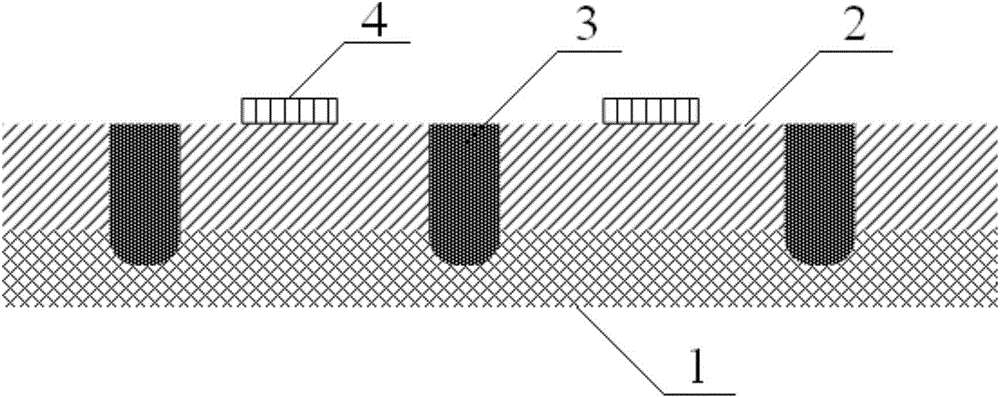

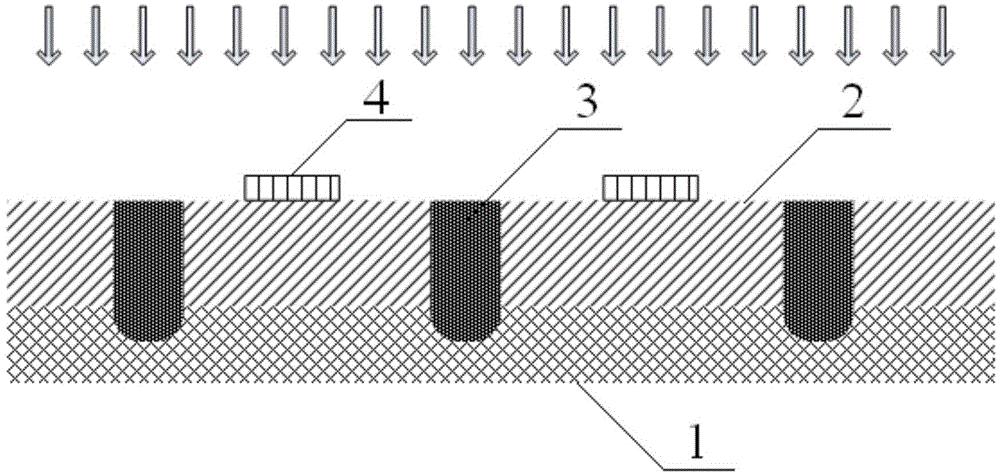

[0045] Such as Figure 1 to Figure 10 As shown, the manufacturing method of a VDMOS device according to an embodiment of the present invention includes the following steps:

[0046] Step 1, forming a gate trench inside the epitaxial layer of the silicon substrate;

[0047] Specifically, the silicon substrate may be a conventional silicon substrate with an epitaxial layer 1 in the art, such as an epitaxial wafer, or the epitaxial layer 1 may be grown on the silicon substrate by a conventional method in the art;

[0048]First, a gate trench mask (ie, a mask layer with a gate trench pattern) can be formed on the epitaxial layer 1, and then the silicon substrate is etched using the mask to form a gate trench inside the epitaxial layer 1. The gate trench, the gate trench can be a plurality of trenches distributed at intervals, for example, an initial oxide layer can be formed on the epitaxial layer 1 as a mask layer, and then by photolithography and etching, on the initial oxide la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More