Manufacturing method for low temperature polycrystalline silicon thin film transistors

A technology of thin-film transistors and low-temperature polysilicon, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as substrate unevenness, brightness deviation of display devices, substrate-to-substrate unevenness, etc., to improve uniformity and enhance The effect of improving productivity and uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

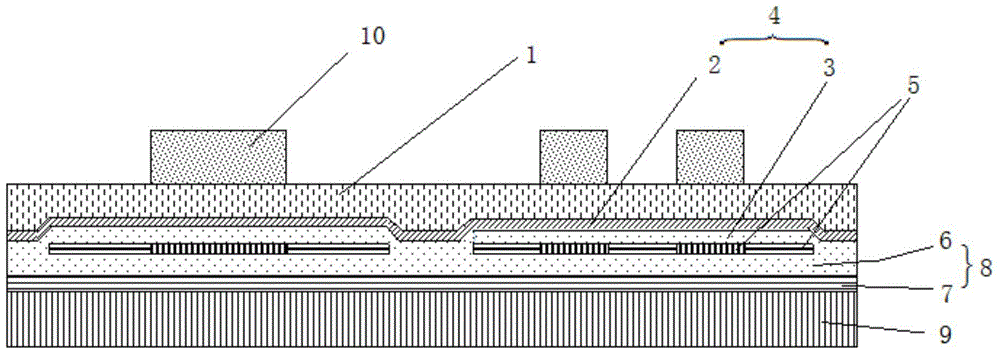

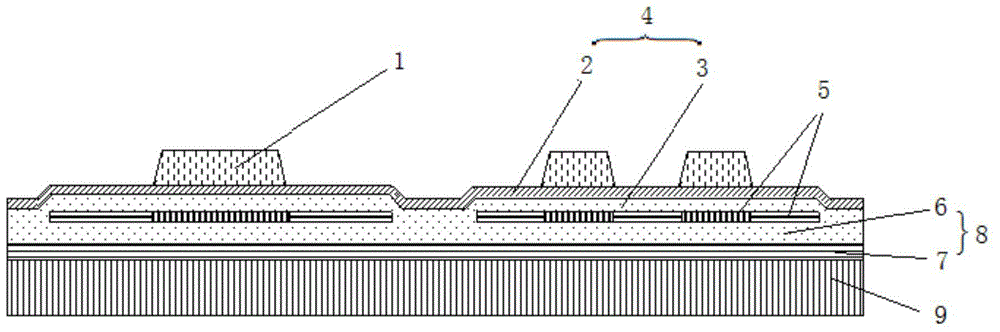

[0051] In the process of dry etching the gate metal, for example, dry etching equipment manufactured by Tokyo Electron Limited (TEL) can be used to implement etching using chlorine gas plasma, and only the metal molybdenum layer is etched to form the gate. Pole, and then demoulding and degumming. Here, the film thickness uniformity of the remaining first silicon nitride layer 2 was measured to be kept below 3% by using an ellipsometer.

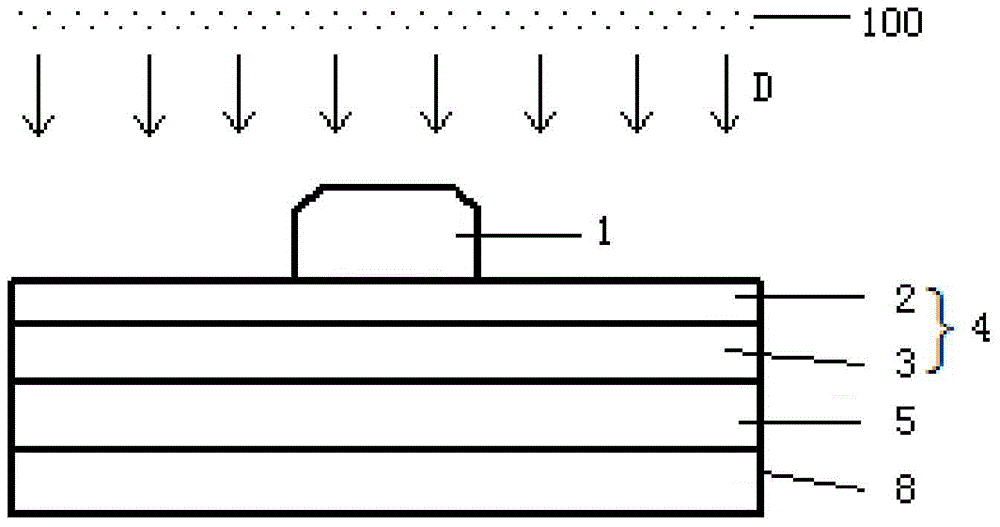

[0052] In the process of penetrating the gate insulating layer, the dopant particles need to penetrate the first silicon nitride layer 2 and the first silicon dioxide layer 3 as the gate insulating layer 4 (respectively equivalent to figure 1 Silicon nitride layer 2 and silicon dioxide layer 3). Implement the lightly doped leakage implantation test, the dopant uses boron ions to incident dopant ions in the ion implantation direction D perpendicular to the substrate, and forms a lightly doped leakage implantation region in the polysilicon layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More