Vertical interconnection structure for three-dimensional package based on aluminum substrates and preparation method thereof

A technology of vertical interconnection and three-dimensional packaging, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc. It can solve the performance requirements of flexible substrates that cannot meet high-temperature service, thermal-mechanical damage of devices, residual stress of solder joints, etc. problem, achieve the effect of improving packaging efficiency and interconnection density, reducing manufacturing cost, and good strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

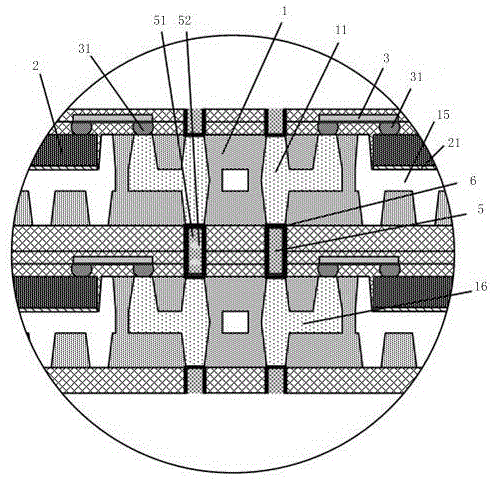

[0073] to combine Figure 1-Figure 2 , this embodiment describes in detail the aluminum substrate-based three-dimensional packaging vertical interconnection structure of the present invention, which includes: functionalized aluminum substrate 1, embedded chip 2, thin film interconnection 3, dielectric layer 4 and intermetallic compound interconnection Line 5, functionalized aluminum plate 1 includes: aluminum through post 11, aluminum half-through post 12, grounding aluminum post 13, chip embedding cavity 14, buried aluminum ground layer 15 and buried aluminum interconnection line 16, chip embedding cavity 14 is set On the upper surface of the functionalized aluminum substrate, it is a concave structure; one side of the embedded aluminum ground layer 15 is connected to the lower end of the chip embedding cavity 14, and the other side is connected to the grounded aluminum column 13; the aluminum through column 11 penetrates the upper and lower sides of the functionalized aluminu...

Embodiment 2

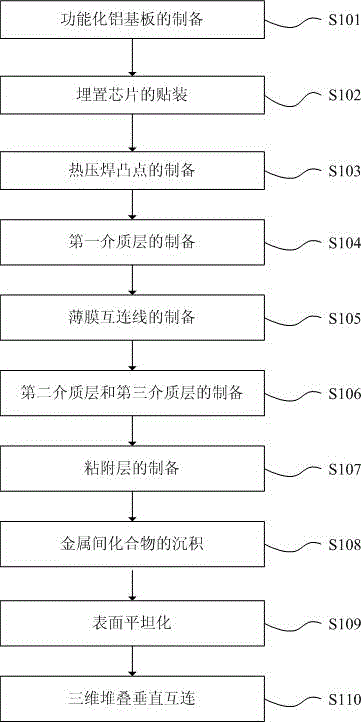

[0079] to combine image 3 - Fig. 4, this embodiment describes in detail the preparation method of the vertical interconnection structure for three-dimensional packaging based on the aluminum substrate of the present invention, which includes the following steps:

[0080] S101: Preparation of functionalized aluminum substrates: provide a pair of polished aluminum substrates, and prepare functionalized aluminum substrates through multiple photolithography and multiple anodic oxidations. The formed functionalized aluminum substrates include: aluminum through pillars 11, aluminum half through pillars 12, Grounding aluminum post 13, buried aluminum ground layer 15 and buried aluminum interconnection 16, aluminum through post 11 penetrates the upper and lower surfaces of functionalized aluminum substrate 1, aluminum half-through post 12 penetrates the upper surface of functionalized aluminum substrate 1, buried aluminum interconnection The connection line 16 is connected to the alu...

Embodiment 3

[0095] The difference between this embodiment and Embodiment 2 is that the thin film interconnection lines are formed in different ways. like Figure 5a , 5b As shown, the thin-film interconnection lines used to connect the embedded chip 2 and the aluminum half-through pillar 12 are directly interconnected through the dielectric hole 411 formed on the first dielectric layer 41 by photolithography and development.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Melting point | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Single layer thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More