High-speed emergent mode code error tester designed based on FPGA technology

A technology of burst mode and technical design, which is applied in the field of optical communication, can solve the problems of increasing output noise, achieve the effect of reasonable design mode, and guarantee precision and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

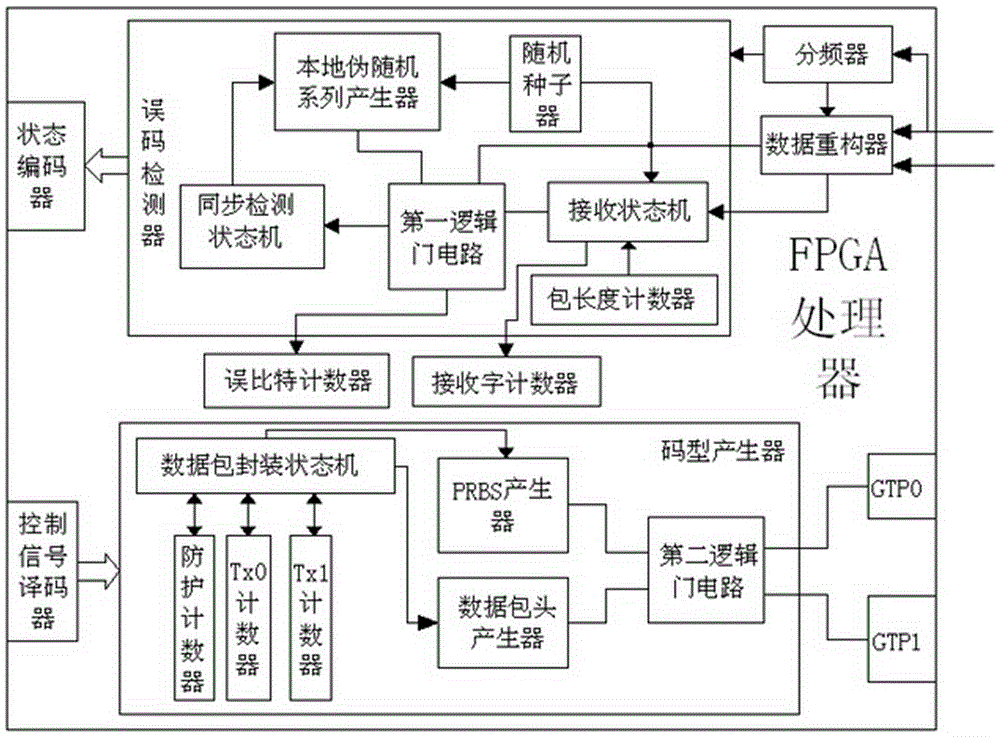

[0050] A high-speed burst mode bit error tester designed based on FPGA technology, a high-speed burst mode bit error tester designed with FPGA technology, can quickly and stably test and record bit errors, and its excellent processing performance, It can effectively ensure the precision and accuracy of error processing, such as figure 1 As shown, the following structure is specially provided: including an FPGA processor, a receiving end processing system and a transmitting end processing system are arranged on the FPGA processor, and the receiving end processing system includes a state encoder, a bit error detector and a counter system, the state encoder is connected to a bit error detector, and the bit error detector is connected to a counting system; the transmitter processing system includes a code pattern generator, a control signal decoder and a GTP solid core, the control signal decoder The encoder is connected to the code pattern generator, and the code pattern generato...

Embodiment 2

[0052] This embodiment is further optimized on the basis of the above-mentioned embodiment, and further to better realize the present invention, such as figure 1 As shown, the following setting structure is specially adopted: a synchronous detection state machine, a local pseudo-random series generator, a random seeder, a first logic gate circuit, a receiving state machine and a packet length counter are arranged in the error detector, so The synchronization detection state machine is connected to a local pseudo-random series generator, the local pseudo-random series generator is connected to a random seeder, and the random seeder is connected to the receiving state machine; the first logic gate circuit is connected to the receiving state machine, and The receiving state machine is connected with the counting system, the first logic gate circuit is connected with the synchronization detection state machine, the first logic gate circuit is connected with the counting system, and...

Embodiment 3

[0054] This embodiment is further optimized on the basis of the above-mentioned embodiment, and further to better realize the present invention, such as figure 1 As shown, the following setting structure is specially adopted: a frequency divider and a data reconstructor are also provided in the receiving end processing system, and the frequency divider is connected to the bit error detector; the data reconstructor is connected to the receiving state machine, so The data reconstructor is connected to the first logic gate circuit through a bus, and the random seeder is connected to the bus and connected to the receiving state machine through the bus.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More