Automatic verification platform and method for on-chip memory management unit fault-tolerant structure

A storage management unit and automatic verification technology, which is applied in the field of automatic verification platform of on-chip storage management unit fault-tolerant structure, can solve the problem of high chip testing cost, improve verification coverage, realize test data randomization, and realize test process automation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

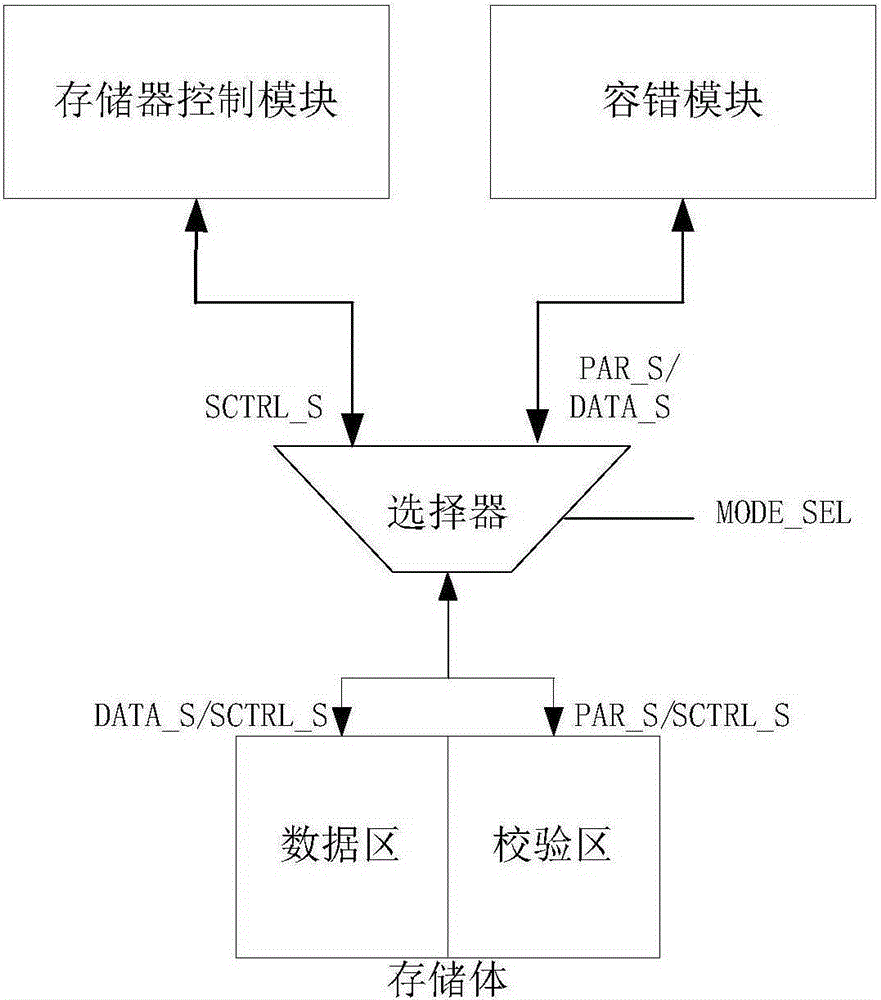

[0037] In the present invention, the fault-tolerant structure of the on-chip storage body adopts two modes of the memory working mode and the fault injection mode to control the data transmission path respectively, wherein in the working mode of the memory, the data area and the check area of the storage body are taken as a whole, through a A set of control signals uniformly controls the input and output of data; in the fault injection mode, the data area and check area of the memory bank are used as two independent storage areas to independently control data input and output through two sets of control signals, which is an on-chip memory bank. The random fault injection verification method of the fault-tolerant structure provides hardware support conditions.

[0038] Fault-tolerant struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More