Formation method of interconnect structure

A technology of interconnect structure and orthosilicate, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems that cannot meet the development requirements of semiconductor technology, poor performance of conductive plugs, etc., and achieve good flatness, Effects of improving filling performance and increasing consumption rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

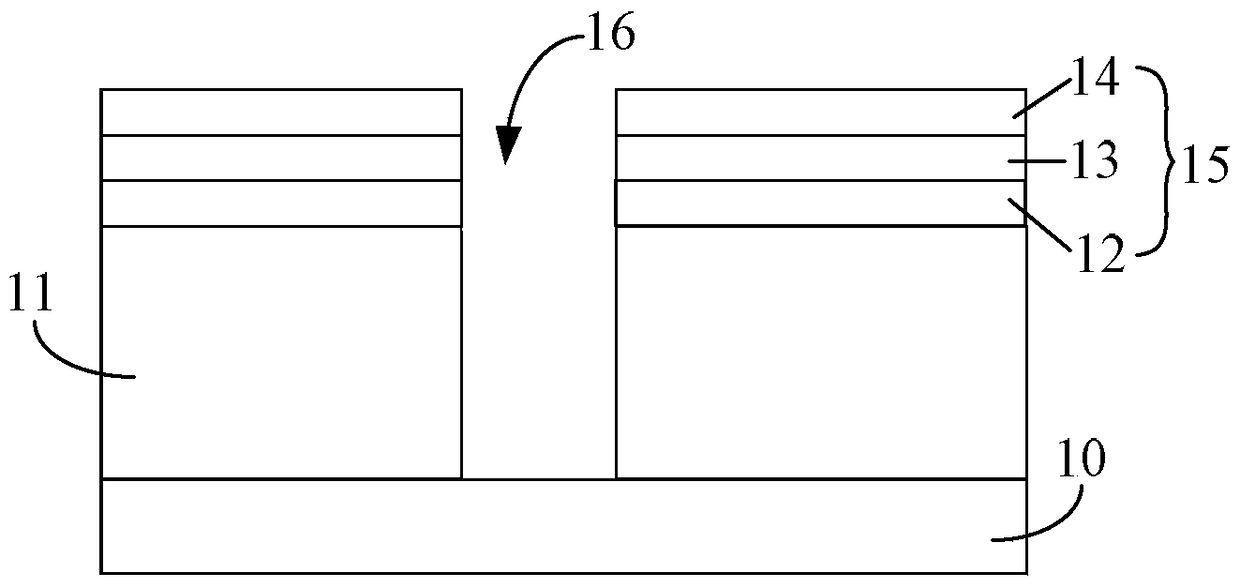

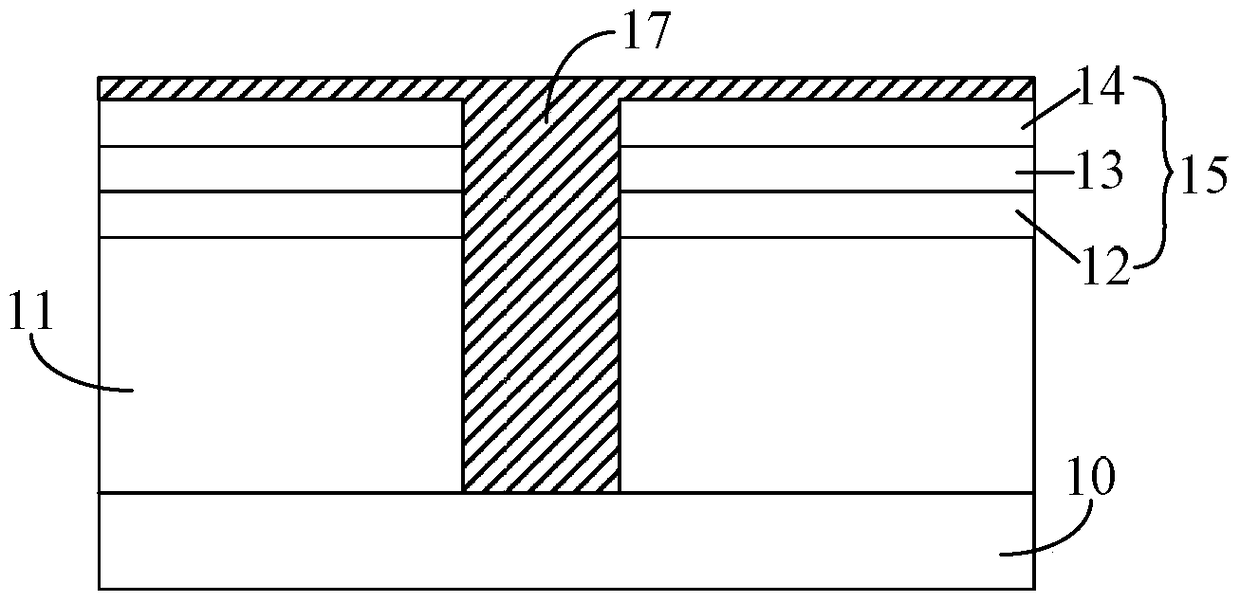

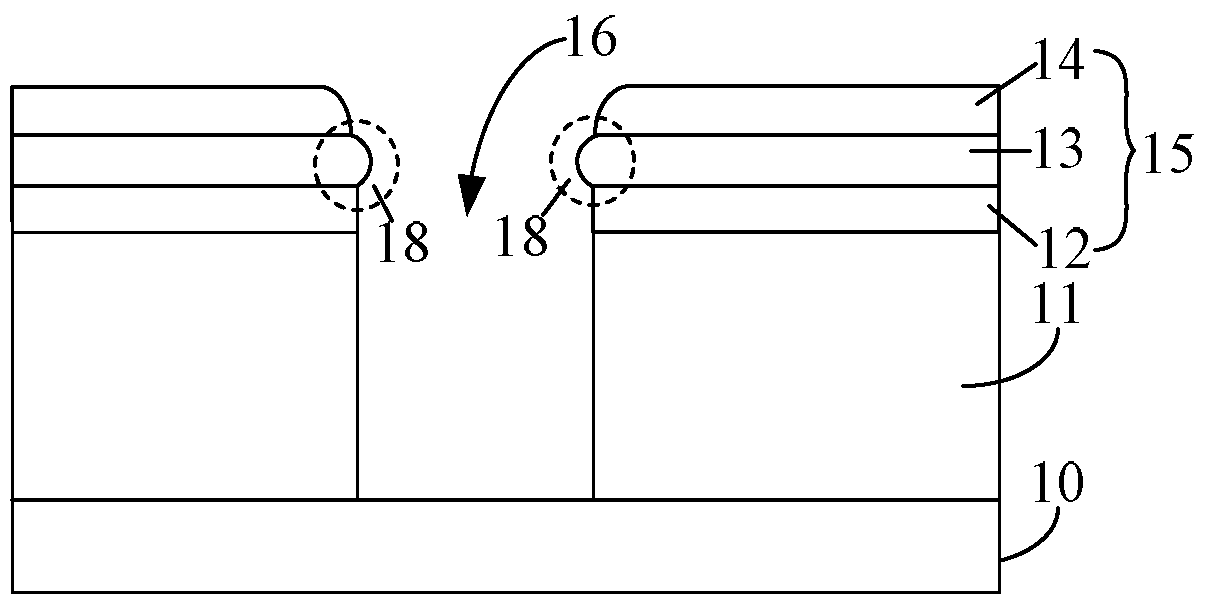

[0048] Figure 4 ~ Figure 15 It is a structural schematic diagram of an embodiment of the method for forming the interconnection structure of the present invention.

[0049] The forming method of the interconnection structure provided in this embodiment includes:

[0050] first reference Figure 4 As shown, a substrate 20 is provided.

[0051] In this embodiment, the base 20 includes: a semiconductor substrate. Alternatively, the base 20 includes a semiconductor substrate and semiconductor components formed in the semiconductor substrate or on the surface of the semiconductor substrate.

[0052] The semiconductor substrate is a silicon substrate, a silicon germanium substrate, a silicon carbide substrate, a silicon-on-insulator (SOI) substrate, a germanium-on-insulator (GOI) substrate, a glass substrate or other III-V compound substrates , The semiconductor substrate material does not limit the protection scope of the present invention.

[0053] A first insulating layer 2...

Embodiment 2

[0100] join Figure 16 and 17 , is a structural schematic diagram illustrating another embodiment of the method for forming the interconnection structure of the present invention.

[0101] The method for forming the interconnection structure of this embodiment and Figure 4 to Figure 15 The similarities of the illustrated embodiments will not be repeated, and the differences are:

[0102] In this embodiment, the silicon oxide mask layer formed on the low-K dielectric mask layer 24 has a single-layer structure, and the forming steps include:

[0103] refer to Figure 16 , first forming a tetraethylorthosilicate layer 361 on the low-K dielectric material layer 24, and then performing an oxygen plasma treatment on the tetraethylorthosilicate layer 361, so that the oxygen plasma and the The tetraethylorthosilicate layer 361 is reacted to form a silicon oxide mask layer 362 .

[0104] In order to reduce the carbon atoms in the silicon oxide mask layer 362, the flow rate of oxy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More