Formation method of transistor

A transistor and dry etching technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that the electrical properties of transistors need to be improved, and the transistor formation process is difficult to control, so as to achieve good appearance and improve electrical properties. performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] It can be known from the background art that the performance of the transistor formed in the prior art needs to be improved.

[0037] Research is conducted on the formation method of the transistor. In one embodiment, taking the transistor to be formed as a CMOS transistor as an example, the formation method of the transistor includes the following steps:

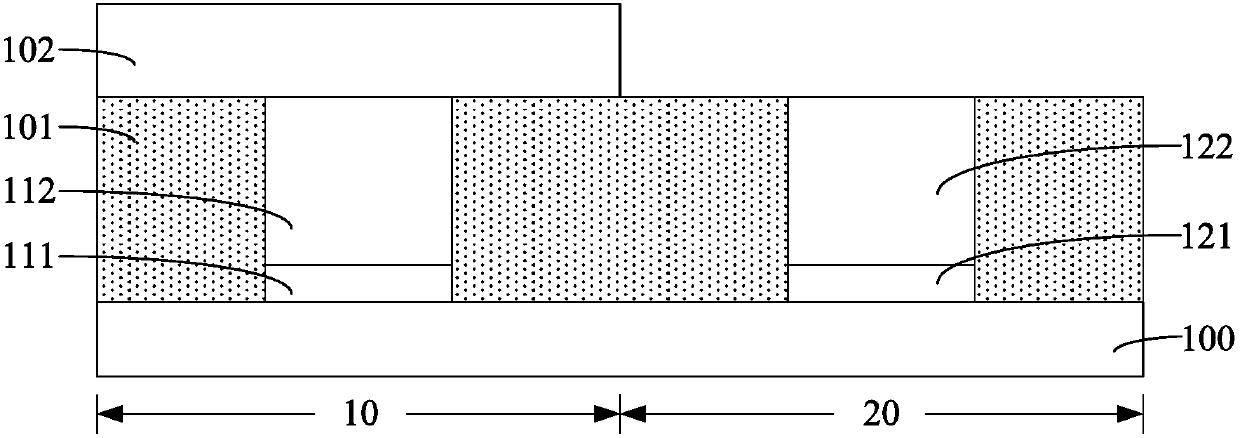

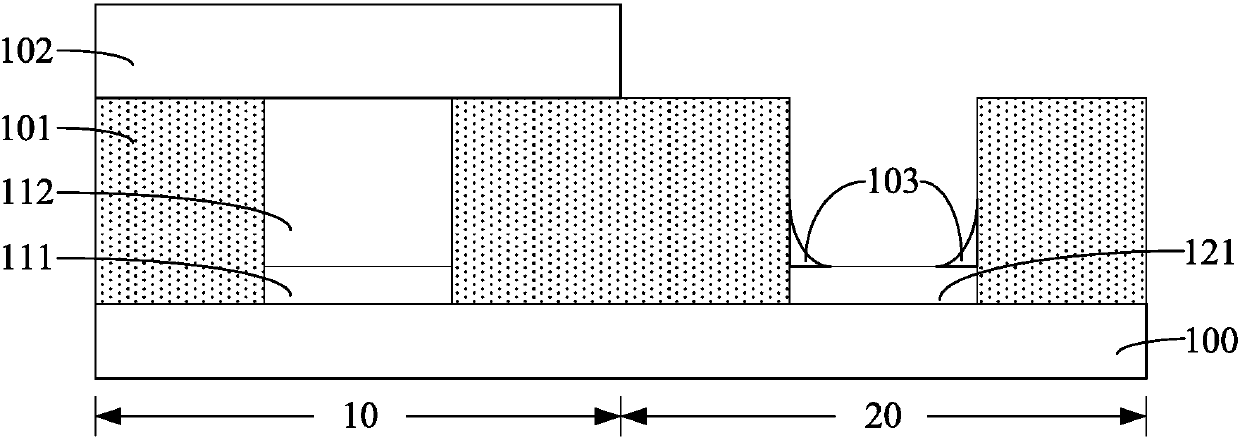

[0038] Such as figure 1 As shown, a substrate 100 is provided. The substrate 100 includes a first region 10 and a second region 20. A first dummy gate structure is formed on the surface of the substrate 100 in the first region 10. The first dummy gate structure includes: A gate dielectric layer 111 and a first dummy gate 112 located on the surface of the first gate dielectric layer 111, a second dummy gate structure is formed on the surface of the substrate 100 in the second region 20, and the second dummy gate structure includes: a second A gate dielectric layer 121 and a second dummy gate 122 located on the surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More