Plasma scribing chip packaging structure and manufacturing method

A production method and plasma technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that affect the dismantling and bonding process, chip drop, and inapplicable temporary bonding packaging solutions, etc., to avoid chip leakage , Easy to hang glue, increase the effect of binding force

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

other Embodiment approach

[0056] In other embodiments, a carrier film is temporarily pasted on the front of the wafer to replace the temporarily bonded carrier. The carrier film has a certain mechanical strength, and one side of the carrier film has a certain adhesive force. Carrier films such as wafer polish films.

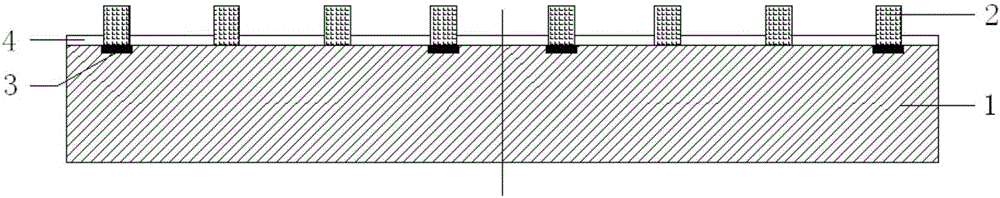

[0057] see Figure 4 , under the support of the carrier plate, the back of the wafer is thinned to near the target silicon thickness. Preferably, it is 20 microns to 40 microns thicker than the target silicon. Thinning methods include one or more of grinding, etching, polishing and the like.

[0058] see Figure 5 , make a mask layer on the back of the thinned wafer, and make an opening at the scribe line position (SL) of the wafer, exposing the silicon substrate at the scribe line position. The mask layer may be a photoresist, and the corresponding opening method is exposure and development.

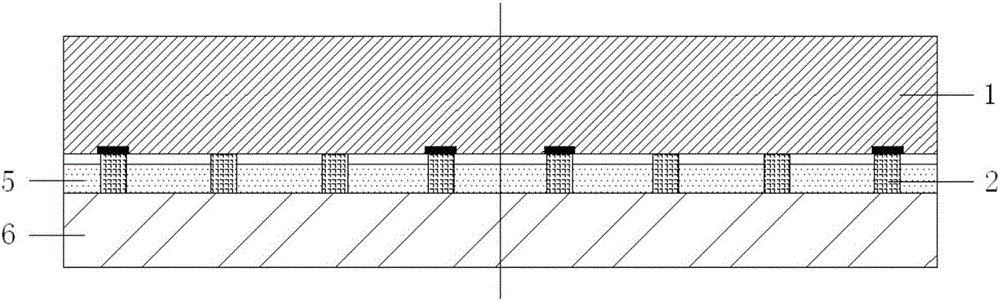

[0059] see Image 6 , plasma dry etching the silicon substrate exposed by the opening, a...

other Embodiment approach

[0064] In other embodiments, a supporting component can be temporarily bonded to the back of the wafer, and the position of the dicing line on the front of the wafer is etched by a plasma dry method to form inclined side walls; the front and side walls of the chip are covered with a passivation layer , removing the passivation layer at the position of the dicing line of the wafer, removing the supporting component on the back, and coating a passivation layer on the back.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More