Method for thinning grid oxide layer and method for manufacturing MOS device

A technology of gate oxide layer and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of avoiding lateral etching, uniform thickness of gate oxide layer, and avoiding lateral damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

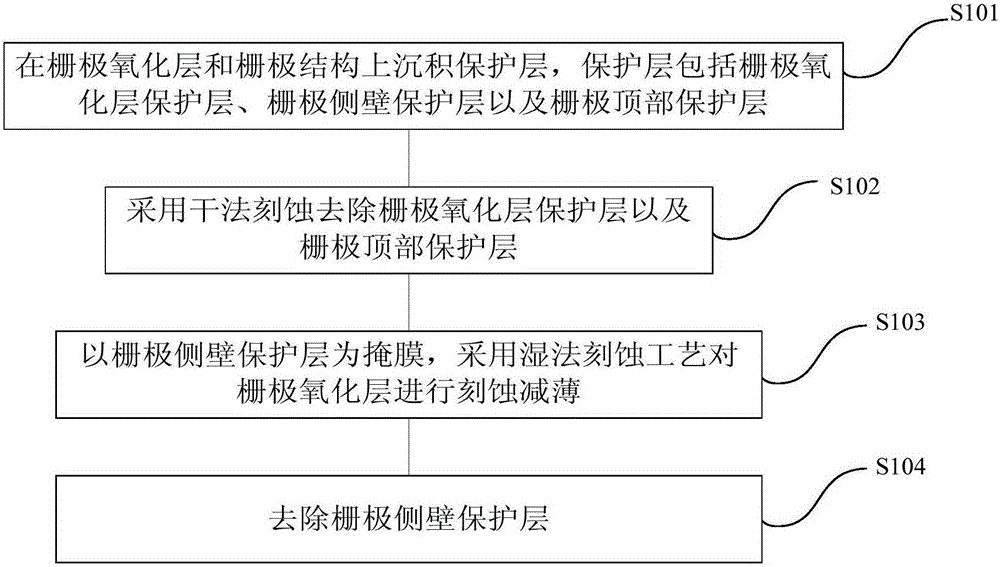

Method used

Image

Examples

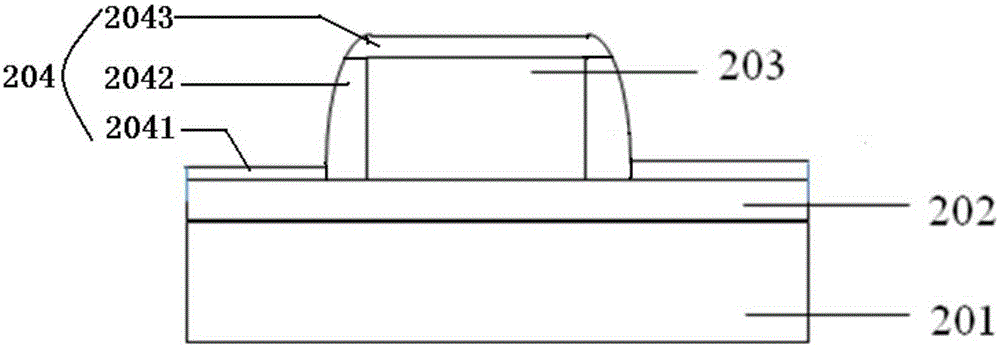

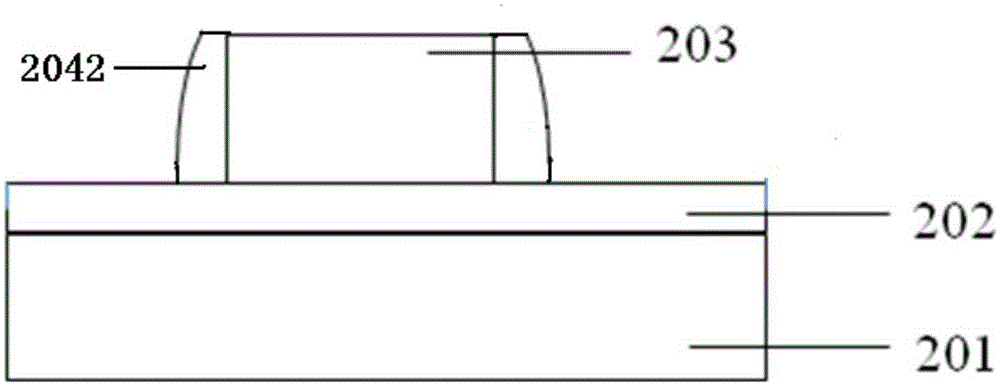

Embodiment 1

[0042] Provide a P-type silicon substrate, deposit a silicon dioxide layer (gate oxide layer) with a thickness of 10 nanometers on the P-type silicon substrate, and then form a source on the silicon wafer through photolithography, etching and electrode material deposition processes Electrode, drain, gate; Deposit a silicon nitride film (protective layer) on the surface of the gate and silicon dioxide layer by chemical vapor deposition process, the thickness of the silicon nitride film is 30 nanometers; remove by dry etching The silicon nitride film on the top of the gate and the surface of the gate oxide layer, the silicon nitride film on the side wall of the gate is retained, the etching gas is oxygen and fluorine-containing gas, the reaction power is 300 watts, and the etching temperature is 50 ° C. The etching time is 15 seconds; immerse the wafer in the HF etching solution, let the HF etching solution react with the gate oxide layer on the substrate for 500 seconds, then gr...

Embodiment 2

[0047] Provide a P-type silicon substrate, deposit a silicon dioxide layer with a thickness of 20 nanometers on the silicon wafer, and then form the source and drain electrodes on the silicon wafer through photolithography, etching and electrode material deposition processes; through chemical vapor deposition The process deposits a silicon nitride film on the surface of the gate and the oxide layer as a gate protection layer, and the thickness of the titanium nitride film is 45 nanometers; the protection on the top of the gate and the surface of the gate oxide layer is removed by dry etching layer, the etching gas is oxygen and helium, the sputtering power is 300 watts, the etching temperature is 50°C, and the etching time is 12 seconds; the wafer is immersed in the HF etching solution, and the HF etching solution and the substrate The oxide layer on the bottom reacts for 500 seconds, and then the gate oxide layer is gradually peeled off. The stripped product leaves the etched ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More