VDMOS device and manufacturing method therefor

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as lower device yield, short circuit of metal layer and polysilicon layer, etc., to avoid connectivity and improve output The effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

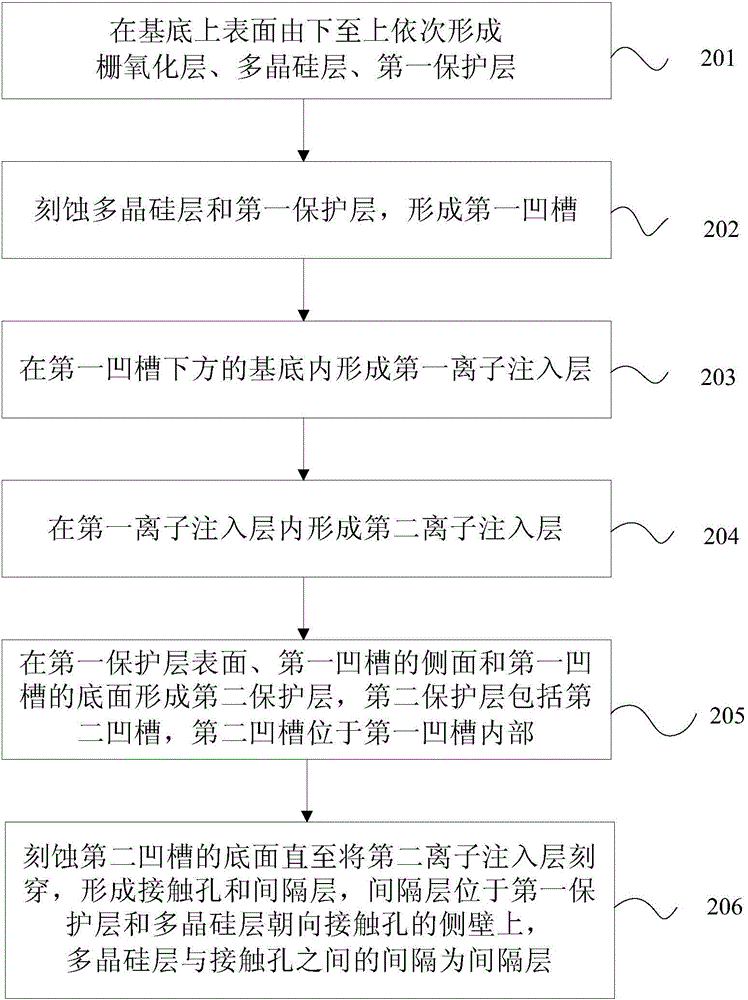

[0013] This embodiment provides a method for manufacturing a VDMOS device. figure 2 It is a flow chart of the manufacturing method of the VDMOS device of the present embodiment, as figure 2 As shown, the VDMOS device manufacturing method may include:

[0014] In step 201, a gate oxide layer, a polysilicon layer, and a first protective layer are sequentially formed on the upper surface of the substrate from bottom to top.

[0015] Specifically, firstly, a gate oxide layer is formed on the upper surface of the substrate by chemical vapor deposition, and the growth temperature is 900°C-1100°C. Of course, the gate oxide layer can also be formed by oxidizing the substrate. The oxidation time can vary with the specific formation of the gate oxide layer. to change the thickness. Further, a polysilicon layer is chemically vapor deposited on the gate oxide layer at a growth temperature of 500°C-700°C, and the first protective layer is formed by oxidizing the surface of the polysili...

Embodiment 2

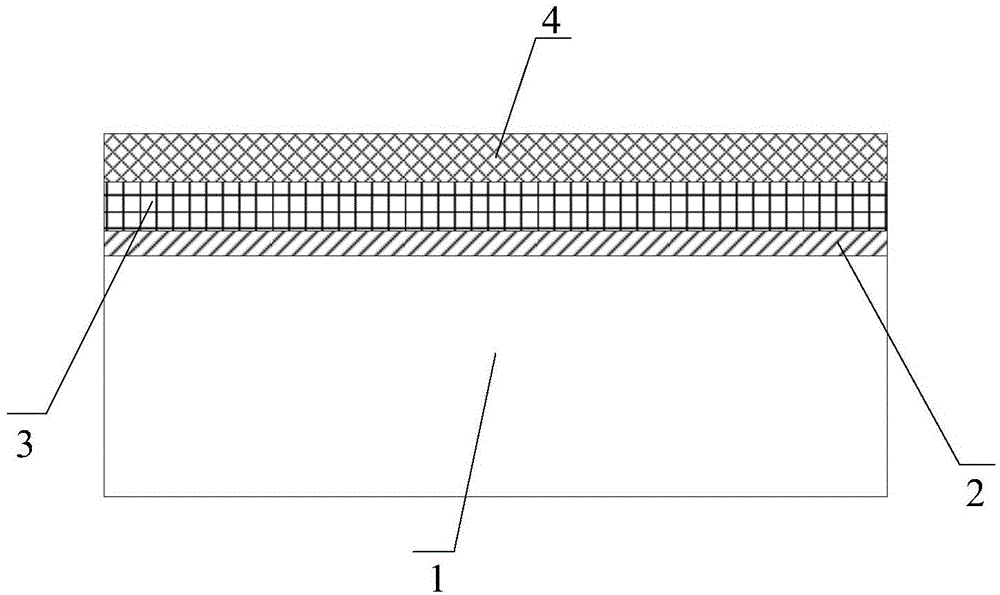

[0028] In order to better describe the first embodiment, this embodiment is based on the above-mentioned embodiment and adds drawings to explain the above-mentioned embodiment. Such as Figures 3A to 3G Show, Figures 3A-3G It is a structural schematic diagram of each step of making a VDMOS device.

[0029] Such as Figure 3A As shown, a gate oxide layer 2 , a polysilicon layer 3 , and a first protection layer 4 are sequentially formed on the upper surface of the substrate 1 from bottom to top. Specifically, the base 1 includes a substrate and an epitaxial layer, and the thickness of the polysilicon layer 3 is 0.2 micron-1.0 micron. Wherein, the thickness of the first protection layer 4 is greater than the thickness of the gate oxide layer 2 .

[0030] Such as Figure 3B As shown, the polysilicon layer 3 and the first protective layer 4 are etched to form the first groove 5 .

[0031] Wherein, the first protection layer 4 is to protect the polysilicon layer 3 and prevent...

Embodiment 3

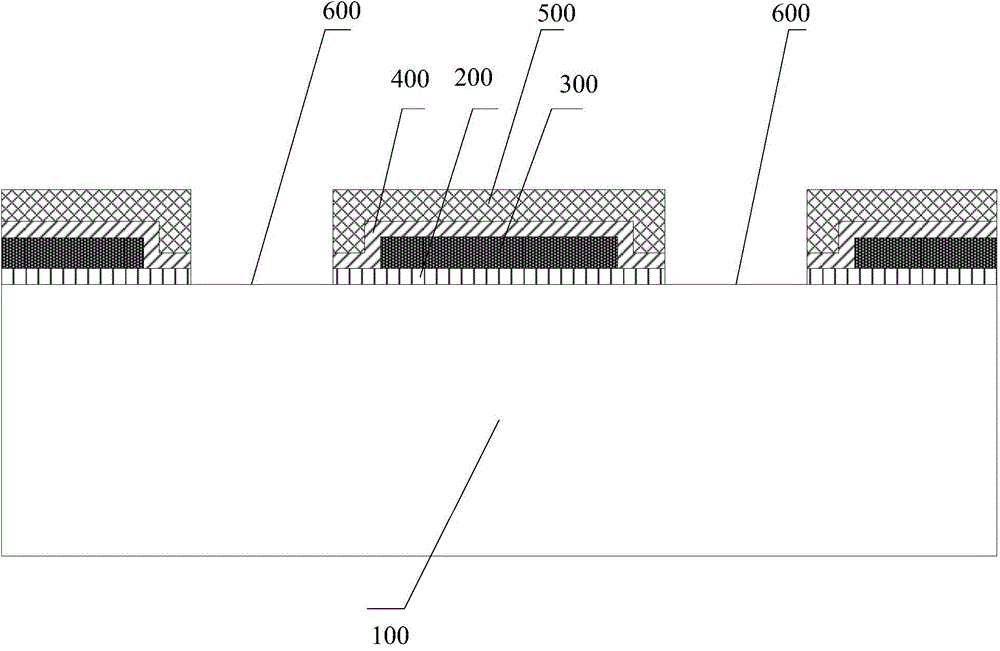

[0040] This embodiment provides a VDMOS device, and the VDMOS device can be manufactured according to the manufacturing method of the VDMOS device in the foregoing embodiments. Among them, such as Figure 3G As shown, the VDMOS device includes: a substrate 1, and a gate oxide layer 2, a polysilicon layer 3, a first protective layer 4, a contact hole 9, a spacer layer 810, and a first ion implantation layer formed sequentially on the upper surface of the substrate 1 from bottom to top. Layer 6, the second ion implantation layer 7.

[0041] Wherein, the contact hole 9 is formed in the gate oxide layer 2 , the polysilicon layer 3 and the first protection layer 4 , and the bottom of the contact hole 9 is located in the substrate 1 . The contact hole 9 penetrates through the gate oxide layer 2 , the polysilicon layer 3 and the first protection layer 4 . Specifically, firstly, the gate oxide layer 2 is formed on the upper surface of the substrate 1 by chemical vapor deposition, an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More