Sealing ring of integrated circuit

An integrated circuit and sealing ring technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of unsatisfactory sealing ring, polysilicon density requirements, and capacitors occupying a large layout area, so as to increase capacitance and avoid uneven surface wrapping. network effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

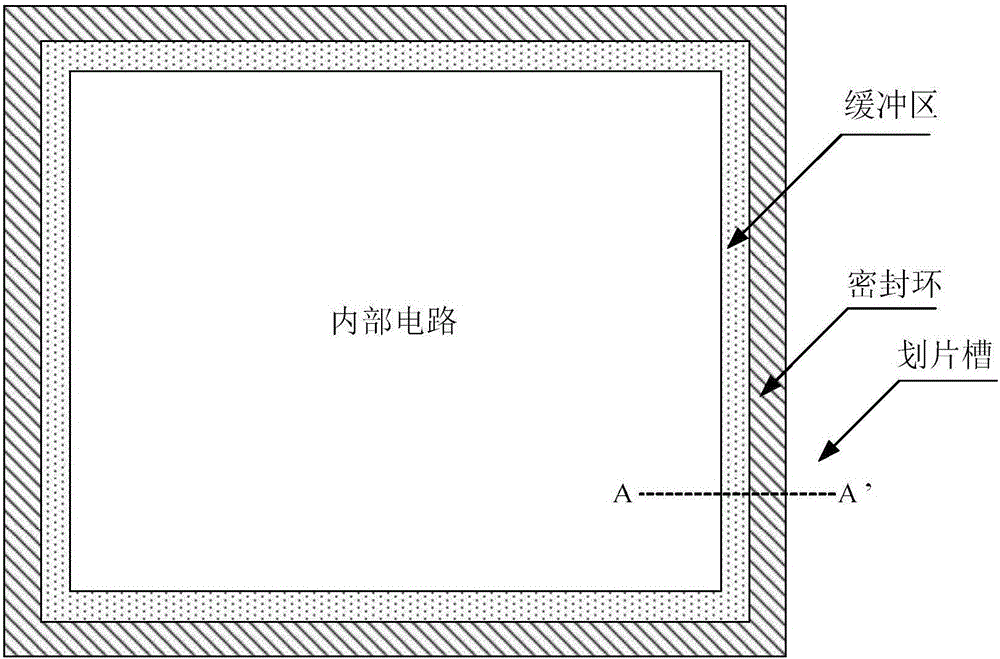

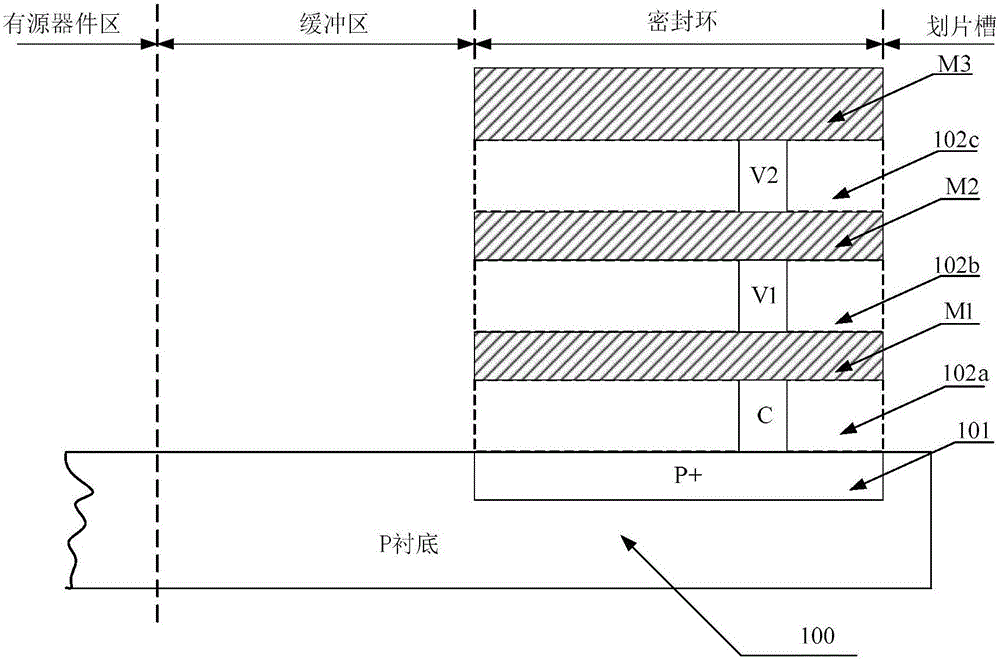

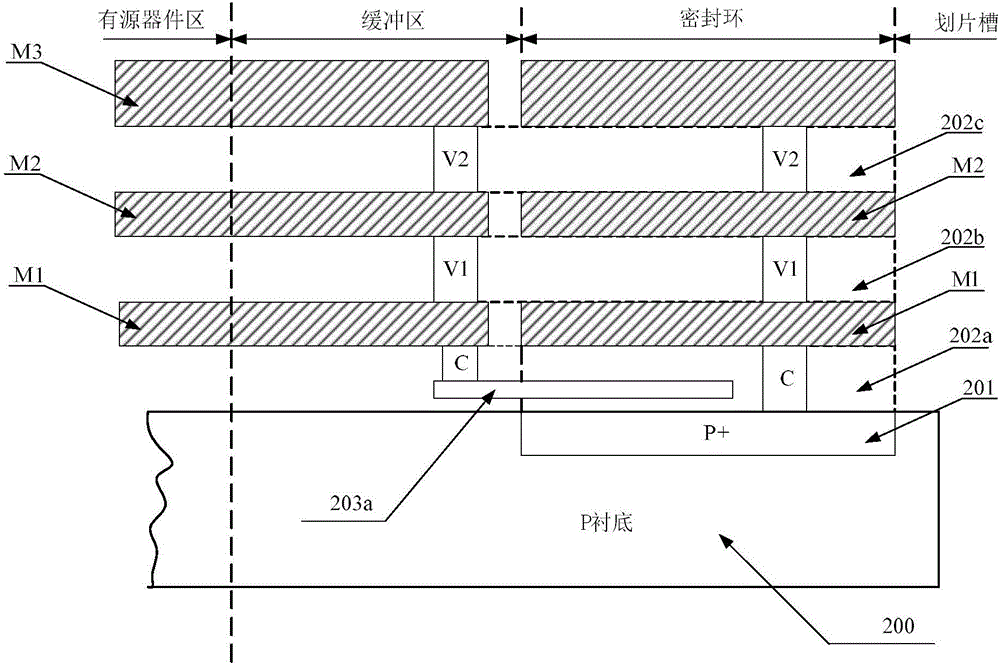

[0043] Such as image 3 As shown, the present invention provides an integrated circuit sealing ring, and the integrated circuit sealing ring at least includes:

[0044] A substrate layer 200 , a doped region 201 formed in the substrate layer 200 , a stacked structure of a dielectric layer and a metal layer formed on the doped region 201 , and a capacitor formed in the stacked structure.

[0045] Such as image 3 As shown, the substrate layer 200 is a P-type material substrate or an N-type material substrate. In this embodiment, the material of the substrate layer 200 is a P-type material, that is, trivalent elements such as boron are doped into the semiconductor ; while N-type materials are doped with phosphorus and other pentavalent elements in the semiconductor.

[0046] Such as image 3 As shown, the doped region 201 is formed on the surface layer of the substrate layer 200, and the doped region 201 is formed by performing heavy doping in the substrate layer 200, and the...

Embodiment 2

[0052] This embodiment provides an integrated circuit sealing ring. The structure of the integrated circuit sealing ring is basically the same as that of the sealing ring in Embodiment 1. The difference is that between any two adjacent metal layers, or the doping A second polysilicon and a third polysilicon are formed between the region and the underlying metal layer in the stacked structure, and the second polysilicon and the third polysilicon are vertically distributed.

[0053] Specifically, as Figure 5 As shown, in this embodiment, a second polysilicon 203b and a third polysilicon 203c are formed in the first dielectric layer 202a above the doped region 201, and the second polysilicon 203b and The third polysilicon 203c is distributed vertically, and the overlapping area of the second polysilicon 203b and the third polysilicon 203c forms a PIP capacitor. The second polysilicon 203b and the third polysilicon 203c are respectively used as the first plate and the second p...

Embodiment 3

[0057] This embodiment provides an integrated circuit sealing ring. The structure of the integrated circuit sealing ring differs from the sealing rings in Embodiment 1 and Embodiment 2 in that a metal plate is formed between any two adjacent metal layers.

[0058] Specifically, as Figure 6 As shown, in this embodiment, a metal plate 204 is formed in the dielectric layer between the second metal layer M2 and the third metal layer M3, and the metal plate 204 intersects with the second metal layer M2 The overlapping area forms the MIM capacitor. The second metal layer M2 and the metal plate 204 serve as the first plate and the second plate of the capacitor respectively, and the capacity of the capacitor is related to the distance between the second metal layer M2 and the metal plate 204 . In this embodiment, the second metal layer M2 serves as the lower plate of the capacitor, and is electrically connected to the substrate layer 200 through the connection hole V1, the first met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More