Manufacturing method for source and drain region contact plug of metal gate transistor

A manufacturing method and metal gate technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as metal gate short circuit, increase process cost, and reduce device yield, so as to reduce alignment accuracy, The effect of improving device yield and reducing lithographic fineness requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

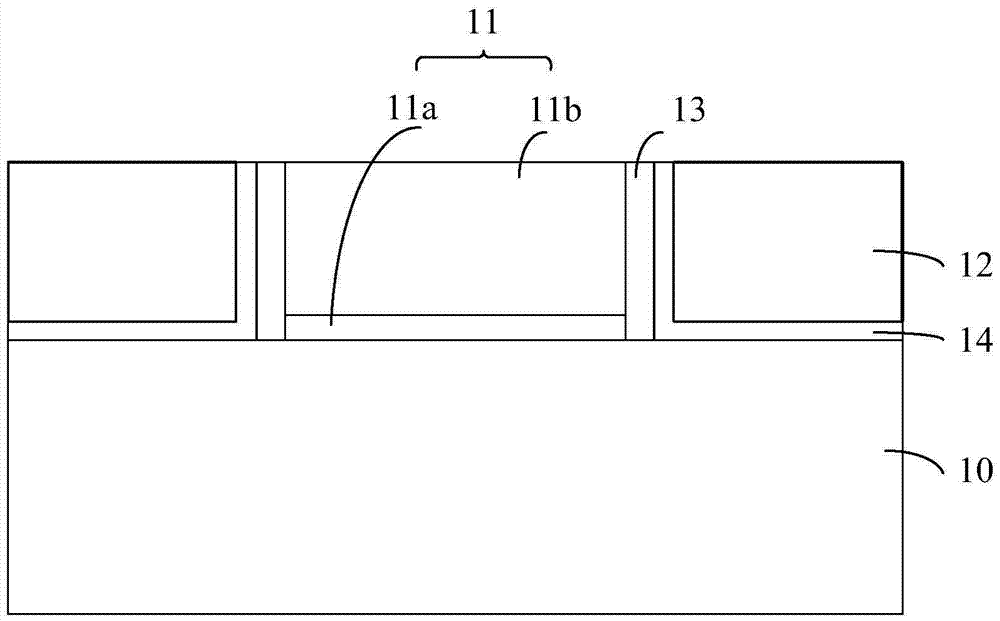

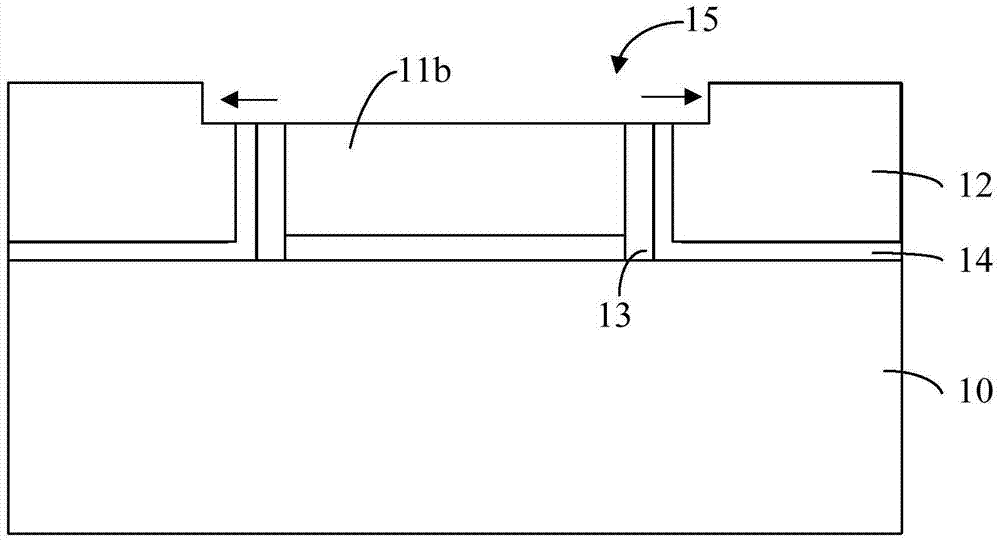

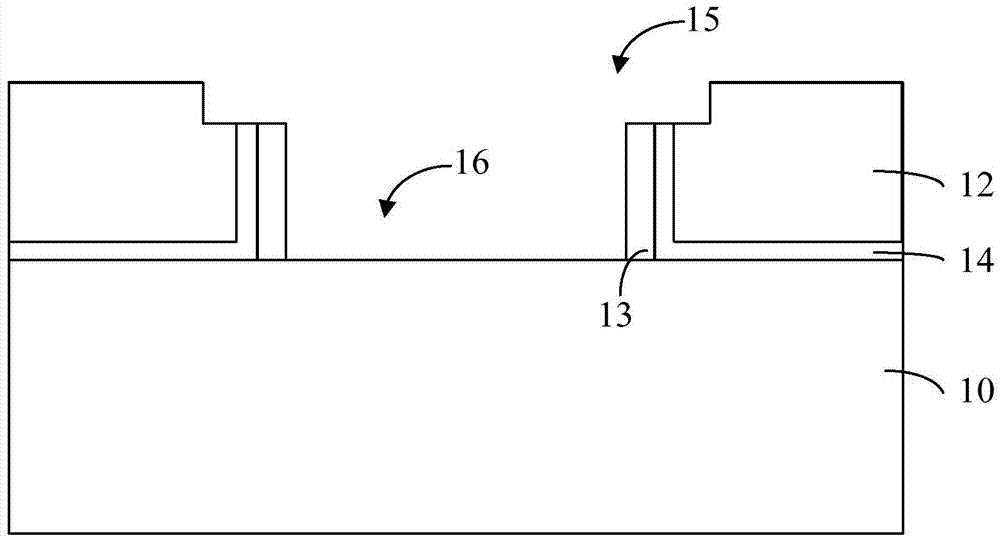

[0042] As mentioned in the background technology, in the prior art, the device yield rate in the manufacture of contact plugs in the source and drain regions of metal gate transistors is low. In order to improve the yield rate, it is necessary to improve the alignment accuracy of the mask degree, which results in higher process costs. In order to solve the above technical problems, the present invention provides a new method for manufacturing contact plugs in the source and drain regions of metal gate transistors. Specifically, an etching stopper layer with both ends wider than the metal gate structure is formed on the metal gate structure. In the process of dry etching to form the contact via hole in the source and drain regions, the etching barrier layer is used to form a protective via hole for the underlying metal gate structure and the dielectric layer, so as to prevent the via hole from exposing the metal gate, thereby avoiding the filling of the via hole. The imported c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More