A wafer-level fan-out stack packaging process method

A packaging process and fan-out technology, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of high manufacturing cost and complicated process, and achieve the effects of saving material costs, reducing manufacturing costs, and reducing packaging manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

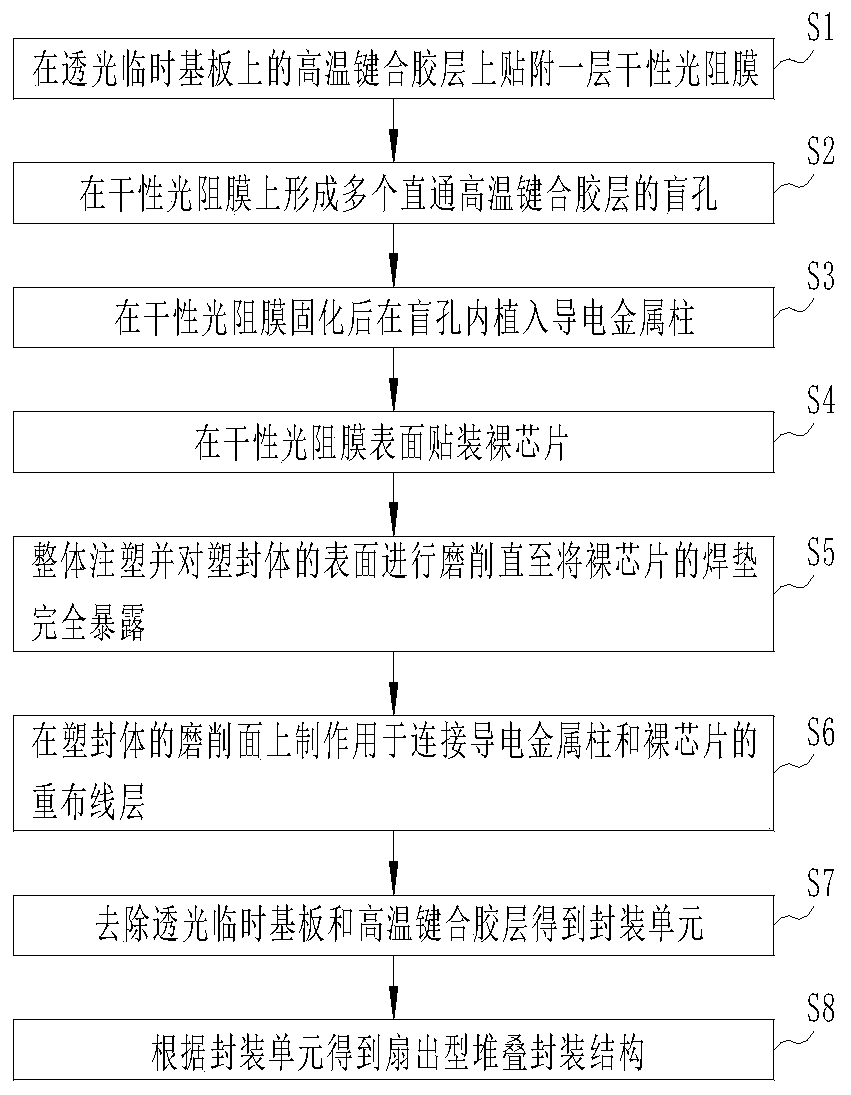

[0039]Embodiment 1 provides a wafer-level fan-out stack packaging process method, such as figure 1 As shown, it includes the following steps:

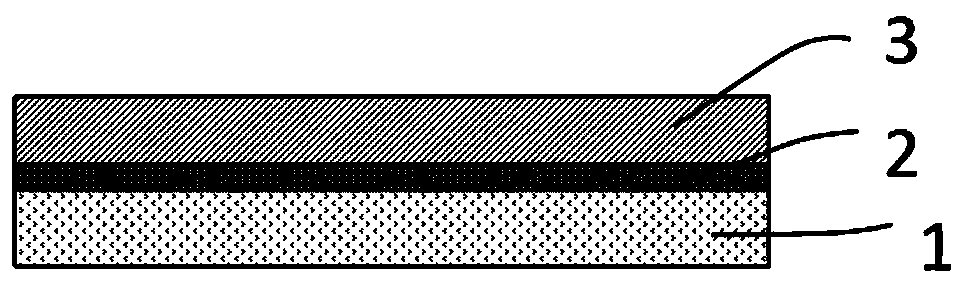

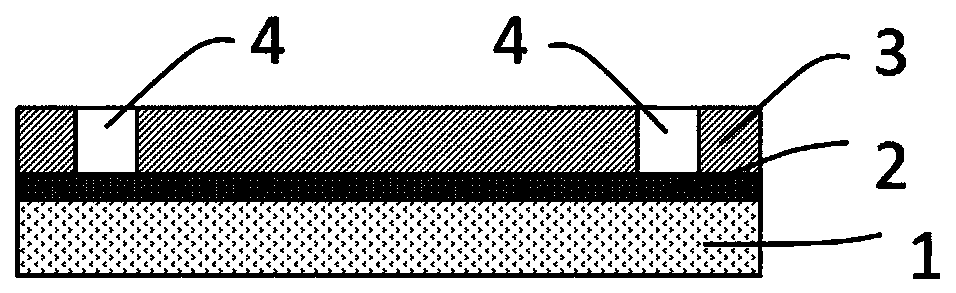

[0040] Step S1: Paste a layer of dry photoresist film 3 on the high-temperature bonding adhesive layer 2 on the light-transmitting temporary substrate 1 . The high-temperature bonding adhesive layer 2 can be cured at a lower temperature and has a stronger adhesive force. When the material is heated to a higher temperature, such as higher than 300°C, the interface between it and the light-transmitting temporary substrate 1 Can lose stickiness. The total thickness of the high-temperature bonding adhesive layer 2 is generally less than 10 μm. The high-temperature bonding adhesive layer 2 can be attached to the surface of the light-transmitting temporary substrate 1 by means of spray coating, spin coating, or film sticking. A layer of dry photoresist film 3 is pasted on the surface of the high-temperature bonding adhesive layer 2, and t...

Embodiment 2

[0055] Embodiment 2 provides a process method of wafer-level fan-out stack packaging, which includes all the steps of embodiment 1, and will not be repeated here to avoid repetition. Embodiment 2 discloses a specific method for stacking more than two packaging units to obtain a fan-out stacked packaging structure, that is, using the micro-bumps of the rewiring layer on the upper packaging unit 21 to interfere with the solidification on the lower packaging unit 22 adjacent to it. The conductive metal pillars exposed on the final dry photoresist film to realize the stacking of package units, such as Figure 13 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More