1.5T depletion-type SONOS non-volatile memory and manufacturing method therefor

A non-volatile, manufacturing method technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problem of large leakage current, uneven doping of the channel region, reduction of carrier mobility and junction characteristics And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

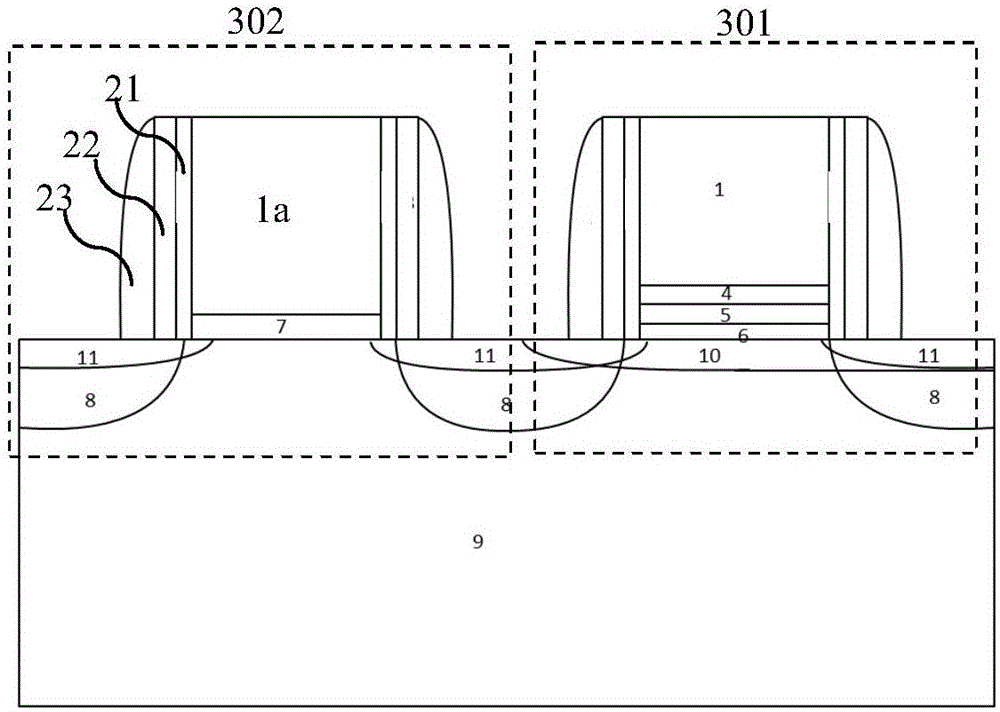

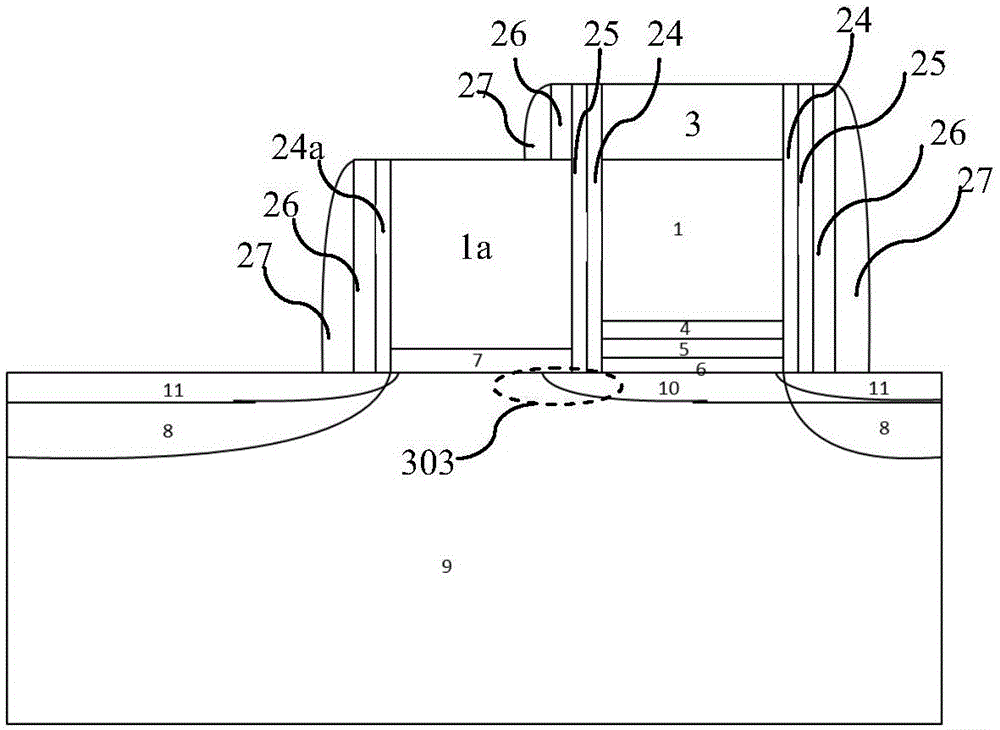

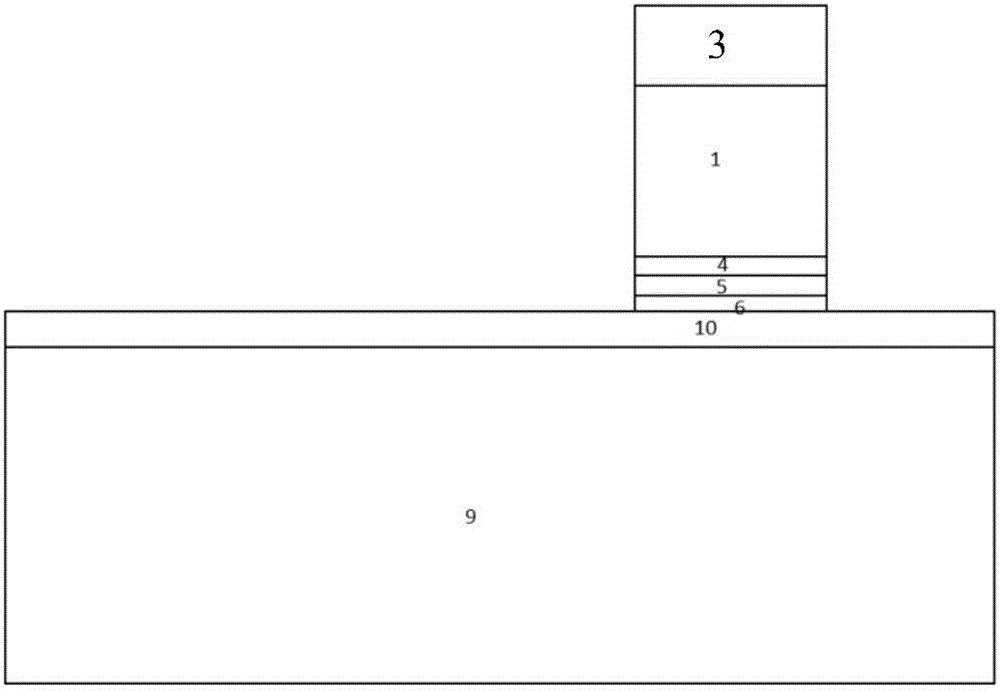

[0073] Such as Figure 5 Shown is a cell structure diagram of the 1.5T depletion-type SONOS non-volatile memory according to the embodiment of the present invention; the cell structure of the 1.5T depletion-type SONOS non-volatile memory according to the embodiment of the present invention includes a SONOS memory transistor and a selection transistor. Figure 5 It also shows a CMOS device integrated with a 1.5T depletion-mode SONOS non-volatile memory. CMOS devices are generally used as logic devices, including PMOS transistors and NMOS transistors. Figure 5 An NMOS tube is shown in .

[0074] The SONOS memory transistor and the selection transistor of the same cell structure share the same N-type doped channel region 102 formed on the surface of the P-type semiconductor substrate 101 . Preferably, the P-type semiconductor substrate 101 is a P-type silicon substrate.

[0075] The gate structure of the SONOS memory transistor includes an ONO layer and a first polysilicon gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com