Conductor structure, capacitor array structure and preparation method

A technology of capacitor structure and conductor structure, which is applied in semiconductor/solid-state device manufacturing, circuits, transistors, etc., and can solve problems such as increased conductivity and limited grain size of polysilicon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

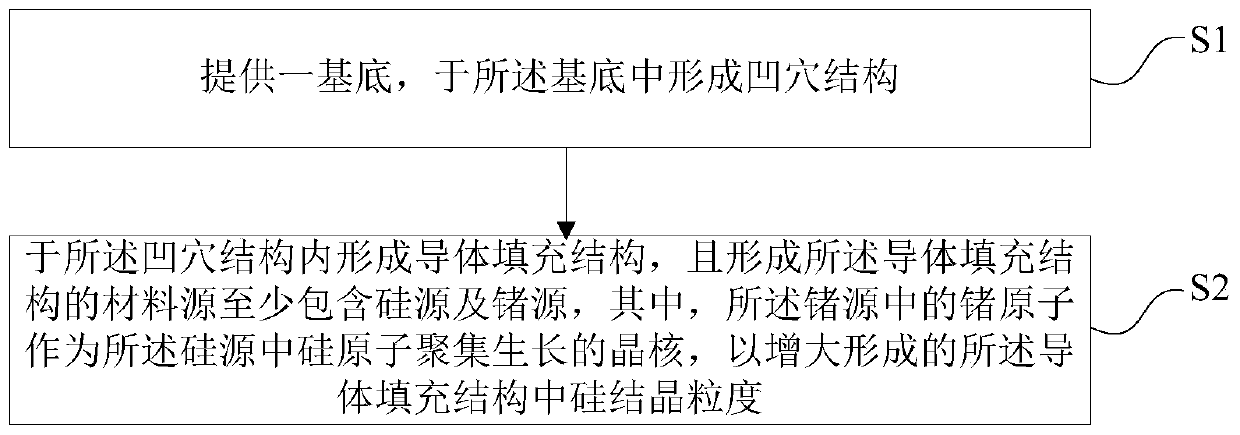

[0115] Such as Figure 1~4 As shown, the present invention provides a method for preparing a conductor structure based on a polysilicon process, comprising the steps of:

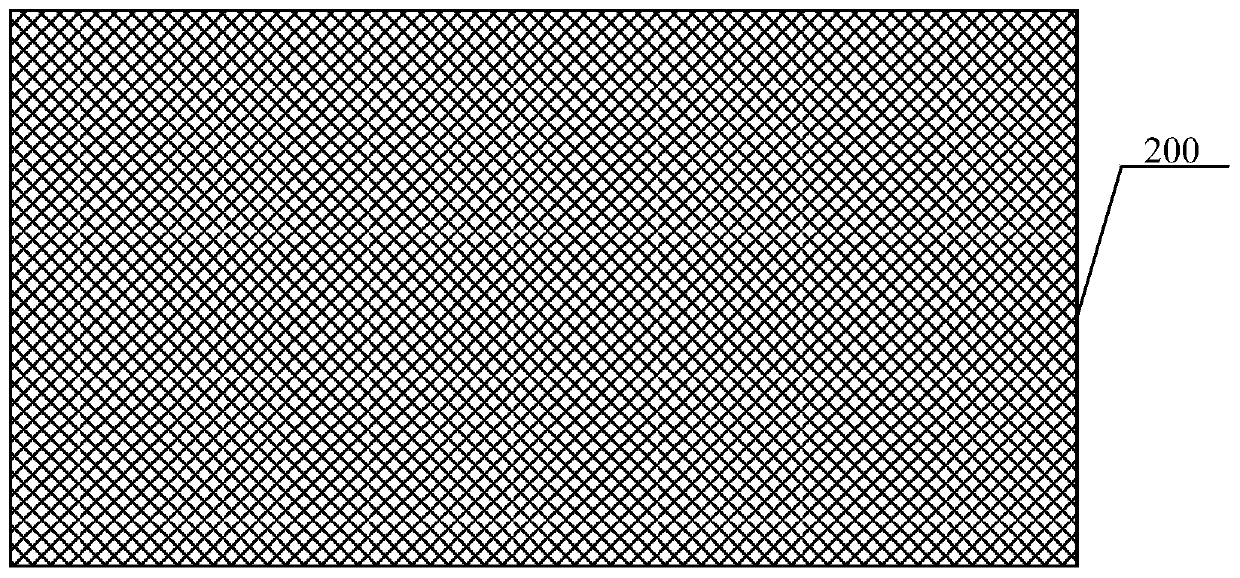

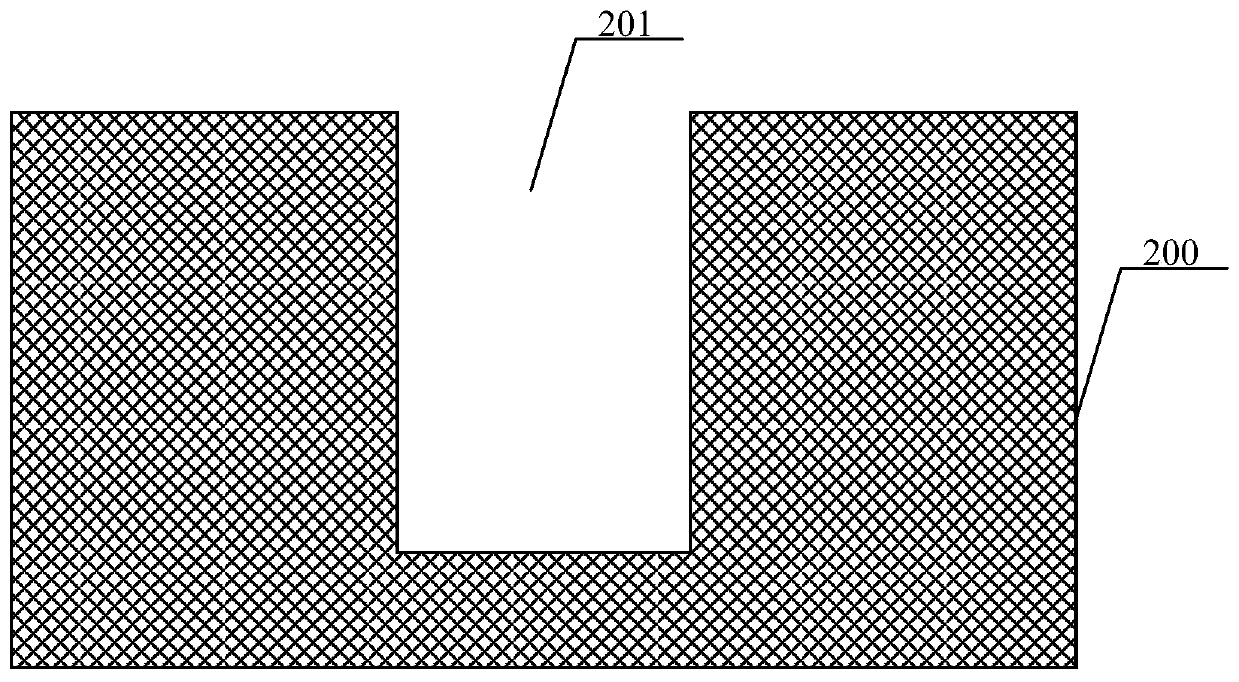

[0116] First, if figure 1 S1 and Figure 2~3 As shown, step 1) is performed, a substrate 200 is provided, and the cavity structure 201 is formed in the substrate 200 .

[0117] Specifically, this step provides a structural basis for subsequent formation of a conductor filling structure, wherein the substrate 200 can be a single material layer, such as a silicon material layer, a silicon-on-insulator material layer, a germanium material layer, and an insulating dielectric layer (such as silicon oxide Layer) etc. are used to open trenches therein and form a conductor filling structure as a metal connection line. Of course, the substrate 200 can also be any semiconductor stacked structure, and it is necessary to open a cavity therein for preparing a conductor filling structure to realize The role of conducti...

Embodiment 2

[0158] Such as Figure 5 As shown, the present invention also provides a method for preparing a capacitor structure array, wherein the preparation of the capacitor structure array in the second embodiment includes the preparation of the conductor structure based on the polysilicon process in the first embodiment, including steps:

[0159] 1) A semiconductor substrate is provided, the semiconductor substrate includes a plurality of capacitive contact nodes located in the memory array structure, and alternately stacked sacrificial layers and supporting layers are formed on the semiconductor substrate;

[0160] 2) forming a patterned mask layer with windows arranged in an array on the structure obtained in step 1), and etching the sacrificial layer and the supporting layer based on the patterned mask layer to form a a capacitive hole corresponding to the window, the capacitive hole exposing the capacitive contact node;

[0161] 3) forming a lower electrode layer on the bottom an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| particle size | aaaaa | aaaaa |

| particle size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More