High-speed receiver circuit of DDR4 standard

A DDR4 and receiver technology, applied in the field of integrated circuit design, can solve the problems of output signal duty cycle process deviation, temperature change and voltage fluctuation, complex DDR4 standard receiver circuit structure, large layout area, etc. performance, reduced component count, and the effect of reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0007] The solutions of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

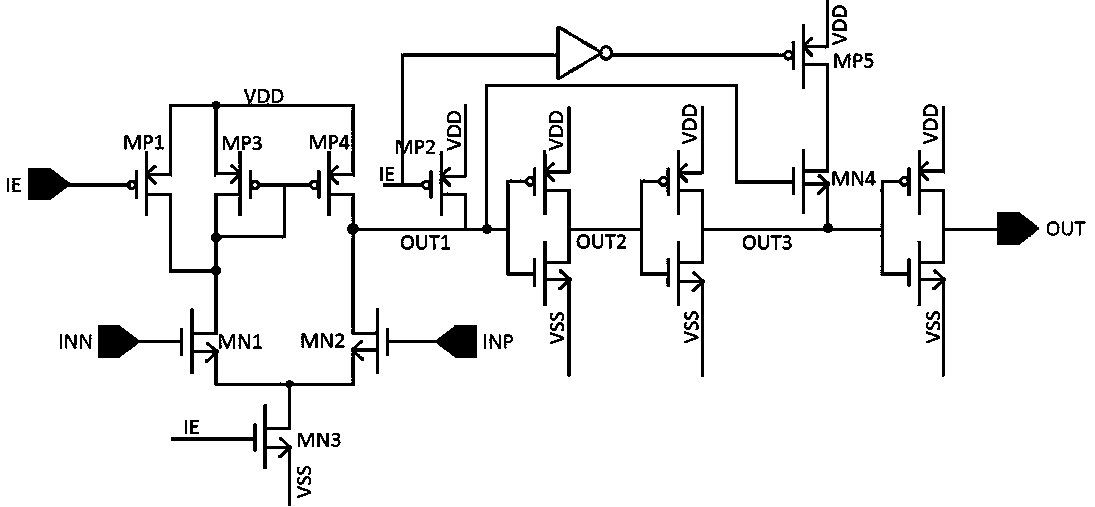

[0008] The DDR4 standard high-speed receiver circuit provided by the present invention includes four parts: a differential amplifier, a buffer, a duty ratio adjustment circuit and an output inverter, wherein:

[0009] (1) The differential amplifier includes two sets of mirror current sources composed of four thin-gate P-type transistors in the core power domain, and a basic differential pair (coupling pair) composed of two thick-gate N-type transistors MN1 and MN2 in the I / O power domain. ), and a tail current source composed of an N-type transistor MN3, which is used to provide bias current for the differential pair, and suppress the influence of the change of the input common mode level on the work of MN1 and MN2 and the output level.

[0010] (2) Buffer: It consists of two sets of inverters, which play the role of buffering ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More