Double-sided capacitor structure and preparation method thereof

A capacitor structure and capacitor technology, applied in the manufacture of capacitors, electric solid devices, semiconductor/solid devices, etc., can solve the problems of short circuit, capacitance value reduction, capacitance area reduction, etc., and achieve the effect of dense density and increased capacitance area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

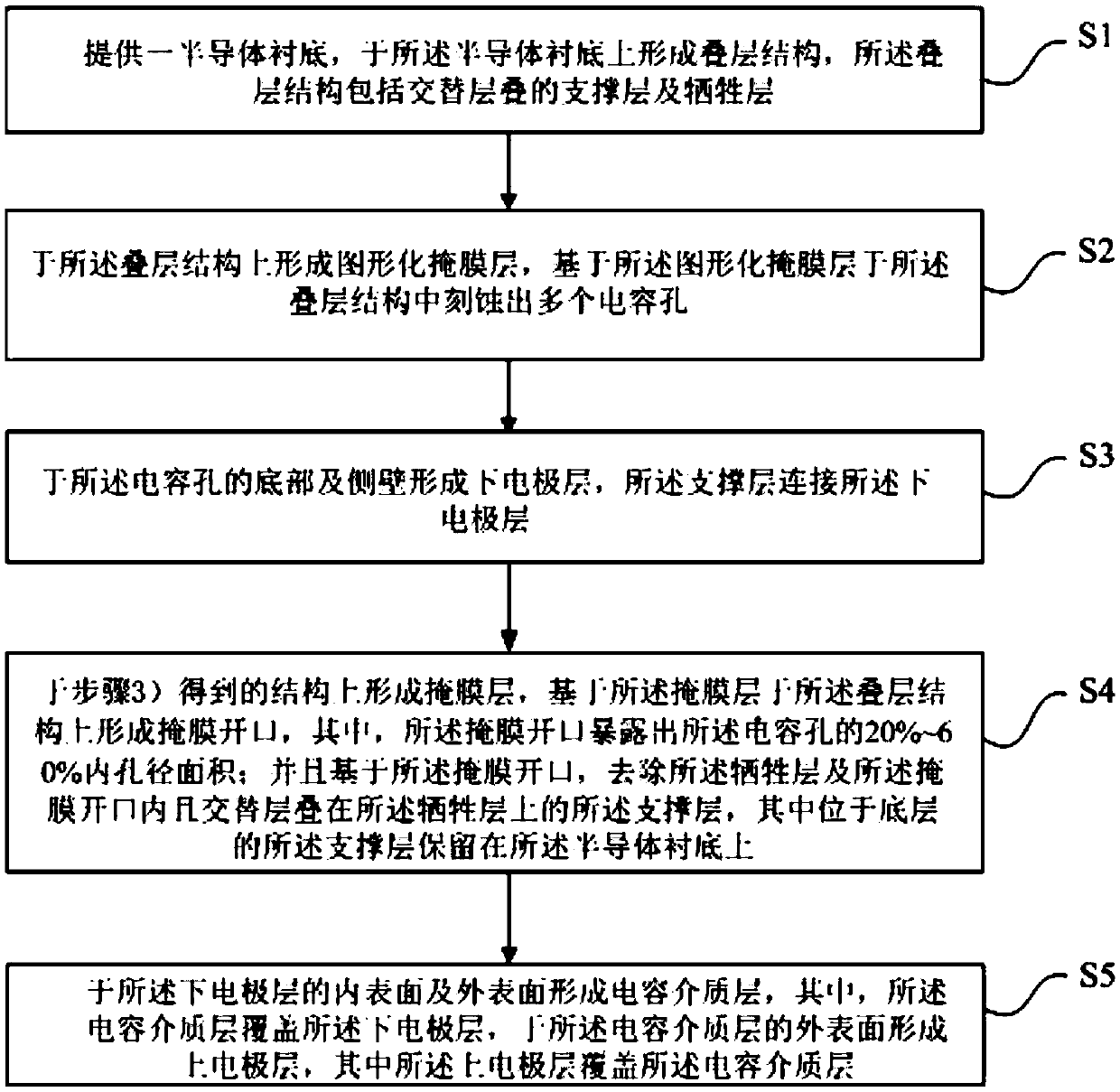

[0123] see figure 2 , the present embodiment provides a method for preparing a double-sided capacitor structure, the method for preparing a double-sided capacitor structure at least includes the following steps:

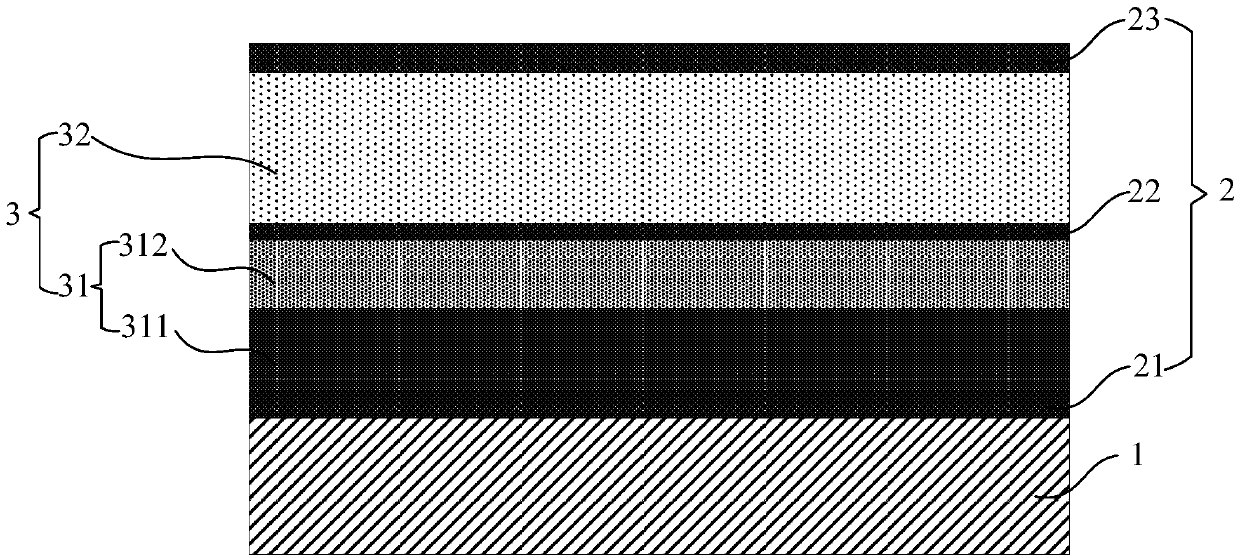

[0124] 1) A semiconductor substrate is provided, and a stacked structure is formed on the semiconductor substrate, the stacked structure comprising alternately stacked support layers and sacrificial layers;

[0125] 2) forming a patterned mask layer on the stacked structure, and etching a plurality of capacitance holes in the stacked structure based on the patterned mask layer;

[0126] 3) forming a lower electrode layer on the bottom and side walls of the capacitor hole, and the supporting layer is connected to the lower electrode layer;

[0127]4) Form a mask layer on the structure obtained in step 3), and form a mask opening on the stacked structure based on the mask layer, wherein the mask opening exposes 20% to 20% of the capacitor hole 60% of the inner apert...

Embodiment 2

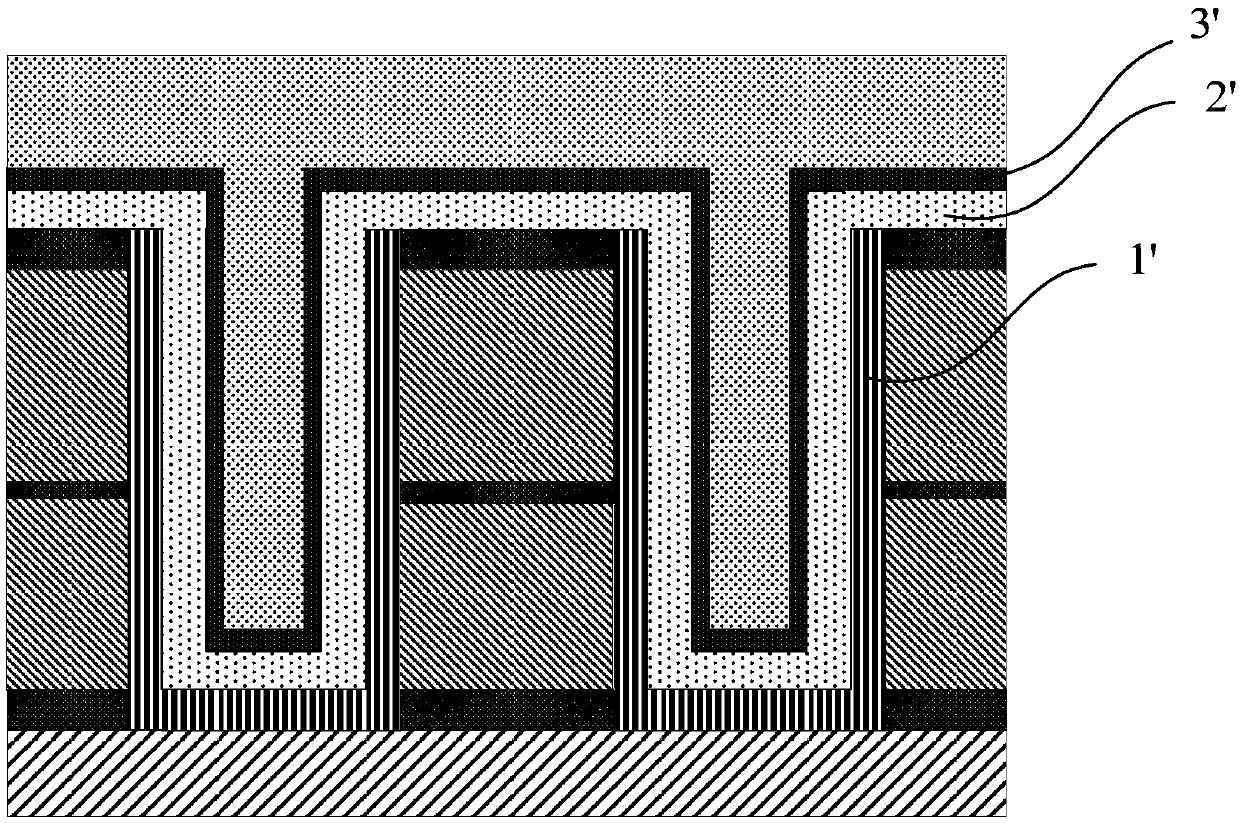

[0169] Please continue to refer to Embodiment 1 Figure 13 , the present invention also provides a double-sided capacitor structure, wherein the double-sided capacitor structure is preferably prepared by the preparation method of the present invention, of course, is not limited thereto, and the capacitor array structure includes:

[0170] semiconductor substrate 1;

[0171] The lower electrode layer 6 is formed on the semiconductor substrate 1, and the cross-sectional shape of the lower electrode layer 6 includes a U shape, wherein the height difference between the two sides of the U-shaped lower electrode layer 6 is 110 nm to 180 nm;

[0172] a capacitor dielectric layer 7 covering the inner and outer surfaces of the lower electrode layer 6;

[0173] The upper electrode layer 8 covers the outer surface of the capacitor dielectric layer 7 .

[0174] As an example, the semiconductor substrate 1 includes several capacitive contact nodes (not shown) in a memory array structure....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More