Manufacturing method of transistor gate

A manufacturing method and transistor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor roughness of the critical dimension of transistor gates, affecting transistor characteristics, etc., to improve characteristics, eliminate influence, and eliminate The effect of differences in gate critical dimensions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solutions in the present invention will be clearly and completely described below in conjunction with the accompanying drawings. Apparently, the described embodiments are part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0025] In an embodiment of the present invention, a method for manufacturing a gate of a transistor is provided. Specifically, the manufacturing method of the transistor gate includes the following steps:

[0026] In step S1, polysilicon, silicon nitride, silicon oxide, an amorphous carbon layer (APF) and an organic coating material layer are sequentially deposited on the isolation region and the active region.

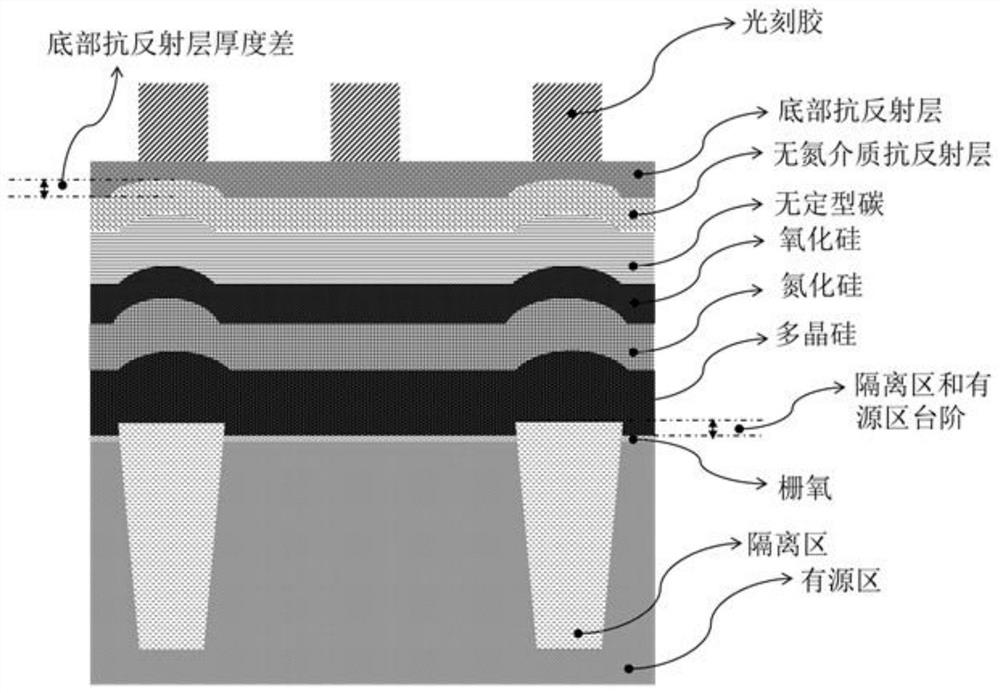

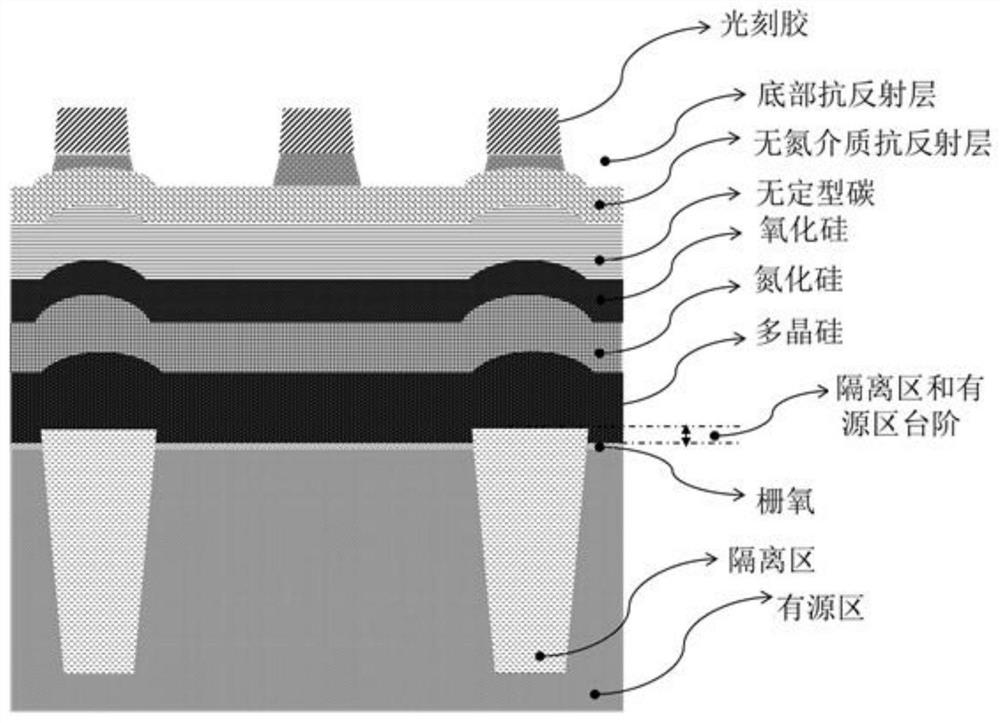

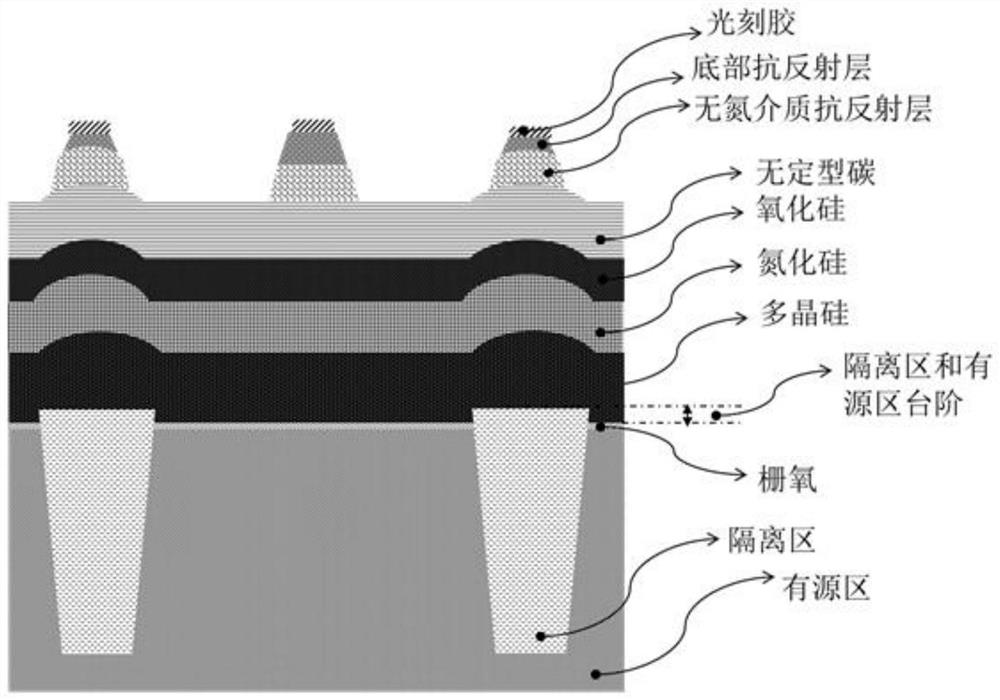

[0027] Specifically, see Figure 4a , Figure 4a It is a schematic diagram of the manufacturing pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More