Fast verification device for MAC (Message Authentication Code) of RSSP-II (Railway Signal Security Protocol-II) based on FPGAs (Field Programmable Gate Arrays)

A verification device and fast technology, applied in encryption devices with shift register/memory, security devices, secure communication devices, etc., can solve the problem of shortened end-to-end communication delay between RBC and in-vehicle equipment, and low processing efficiency of software programming. High reliability and security, increase data throughput, and shorten verification time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The core idea of the present invention is to use FPGA as a coprocessor, design a kind of RSSP-II protocol MAC code rapid verification device, combine the advantage of FPGA parallel operation, liberate CPU system resource, be conducive to RBC, vehicle-mounted, TSRS equipment performance improvement, improve data throughput. The specific implementation method of this FPGA-based RSSP-II protocol MAC code fast verification device is as follows.

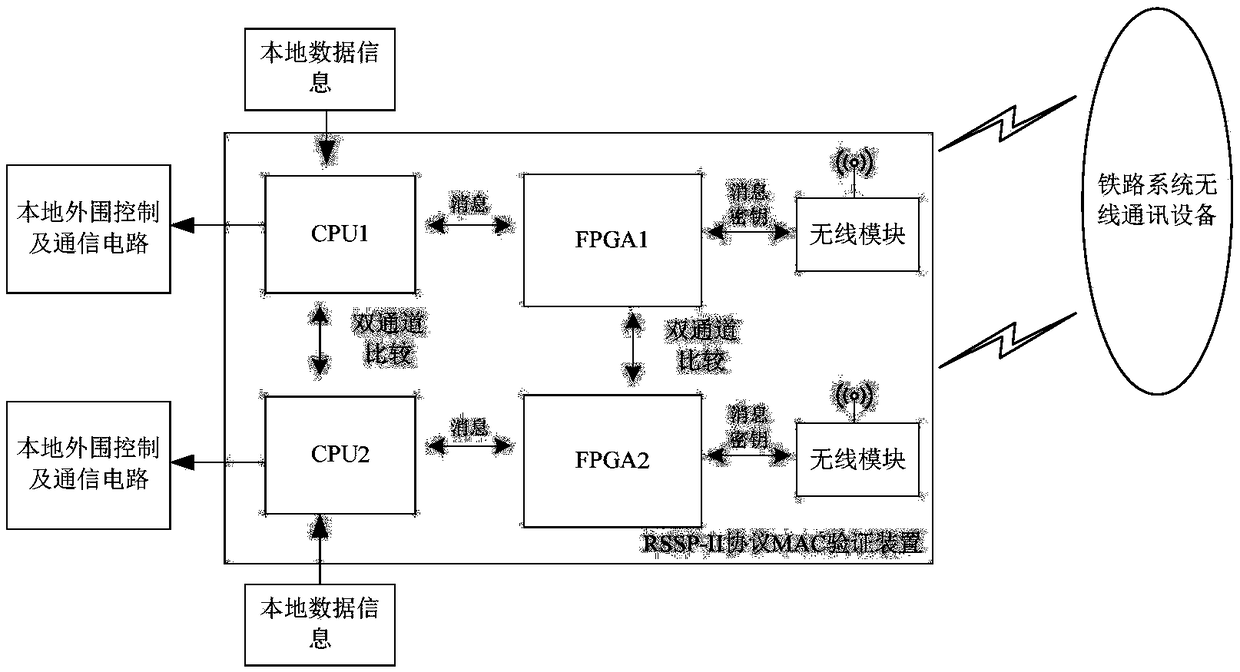

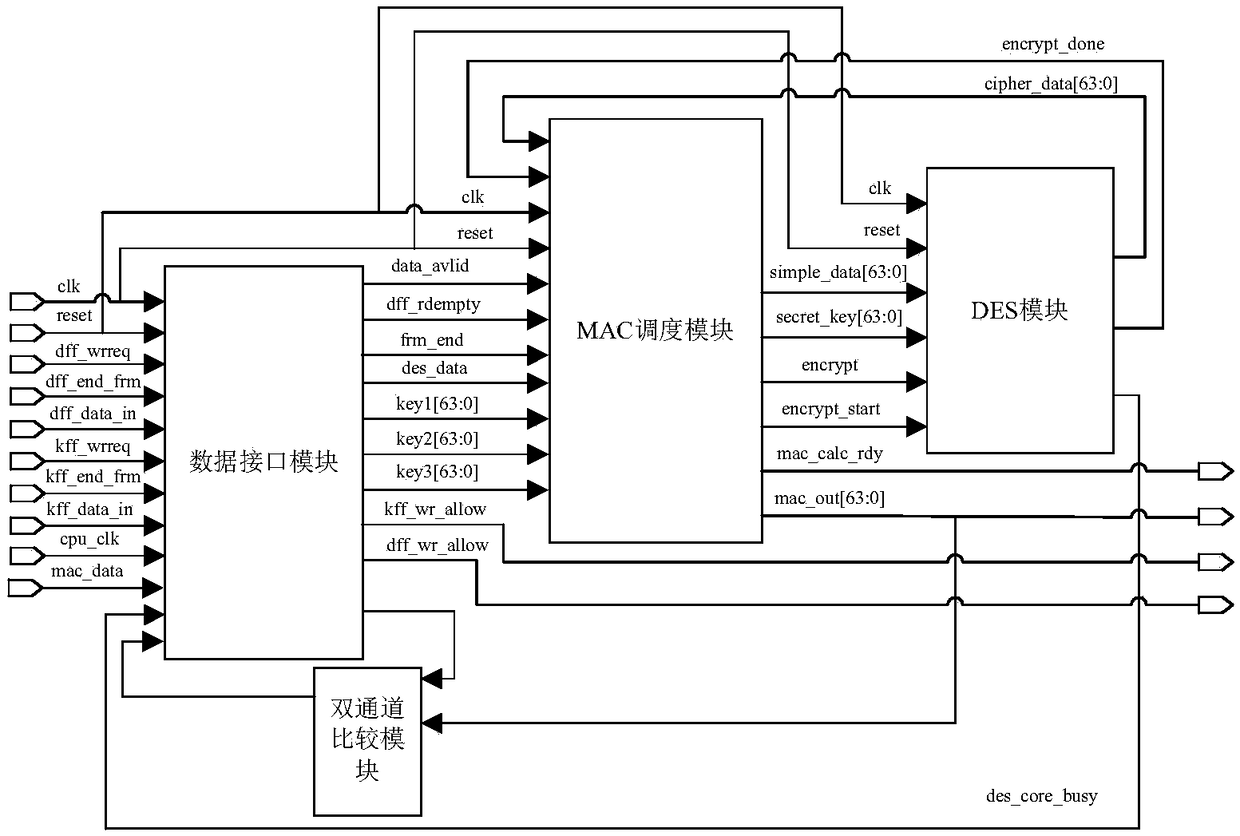

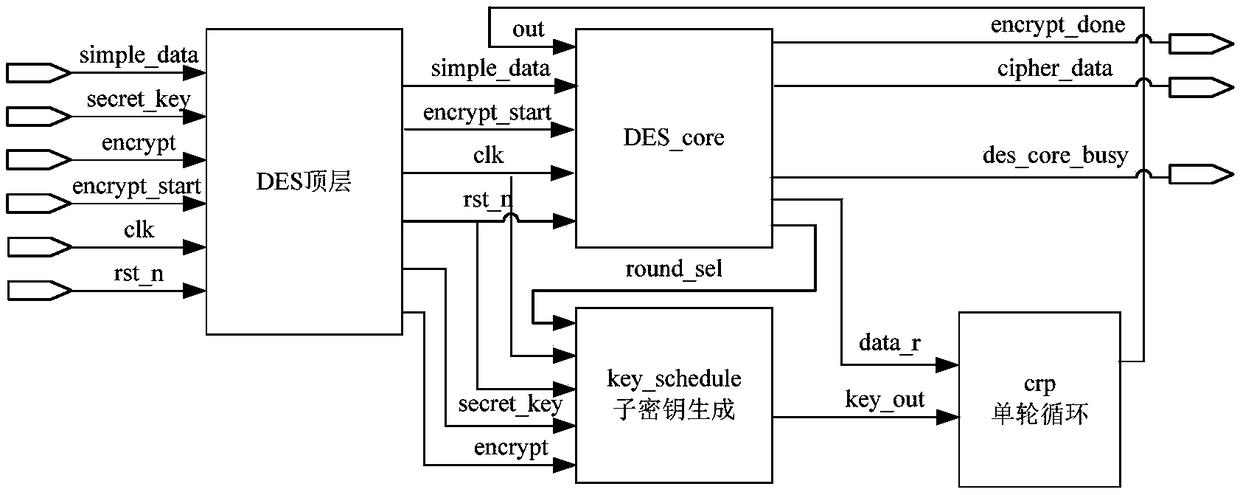

[0028] see figure 1 , a schematic diagram of the connection of the RSSP-II protocol MAC code fast verification device is given. Described wireless module comprises wireless transceiver device, communicates with FPGA through on-chip UART; Programmable logic array FPGA carries out hardware programming, comprises figure 2 The module division shown includes data interface module, MAC scheduling module, DES module, and dual-channel comparison module; channel comparison between FPGAs is through on-chip UART; 16-bit parallel bus is u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More