A Gige Vision interface image transmission system and method based on FPGA

A transmission system and transmission method technology, applied in the field of FPGA-based GigeVision interface image transmission system, can solve the problems of short transmission distance, high hardware cost, high operating power consumption, etc., to improve energy efficiency ratio, reduce hardware cost, reduce operation The effect of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

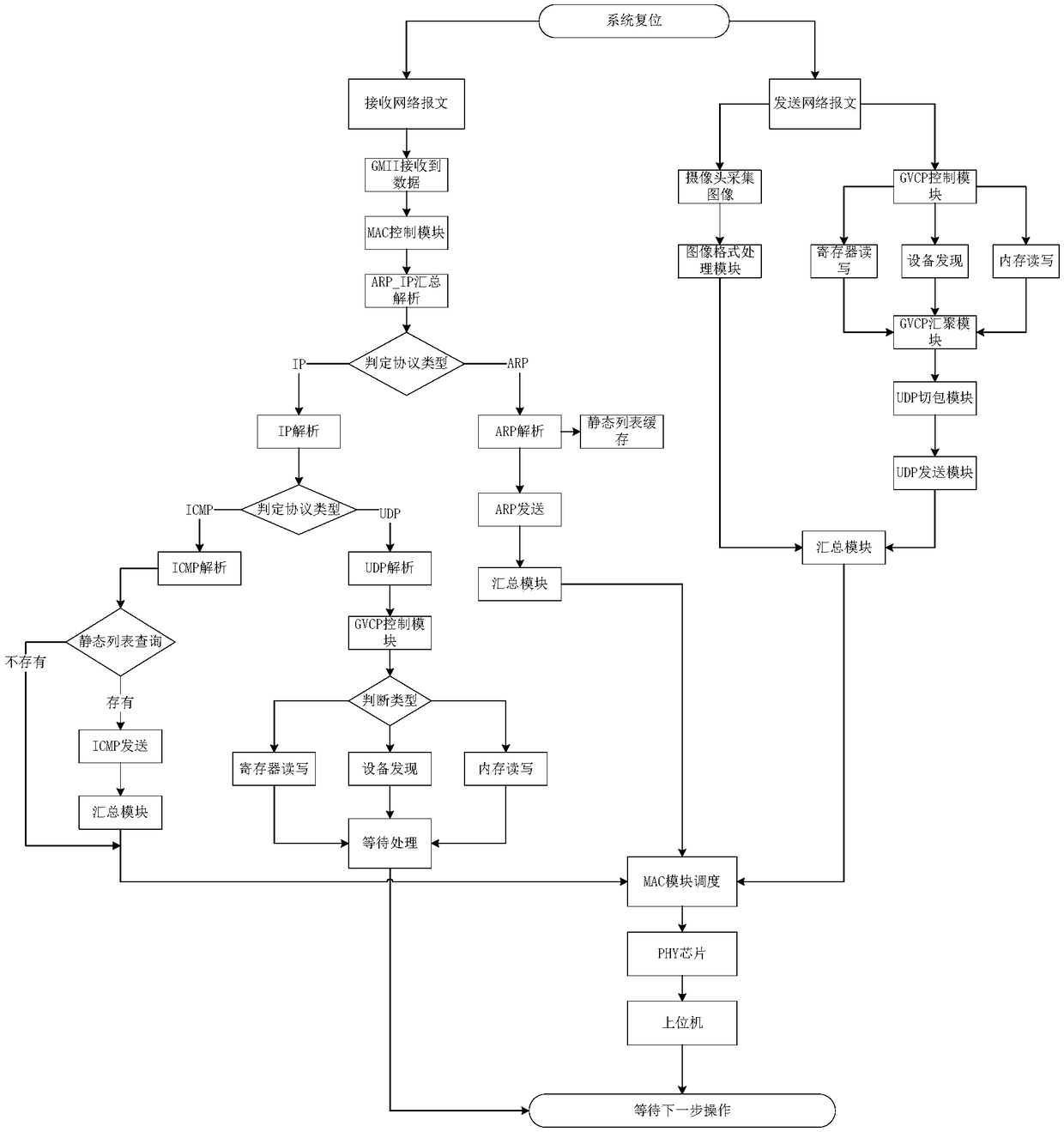

[0051] In order to improve the shortcomings of the traditional Gige IP core, such as large logical resource consumption and high hardware cost, the present invention simplifies the protocol to design a support control message protocol (Internet Control Message Protocol, ICMP), Address Resolution Protocol (Address Resolution Protocol, ARP), User Datagram Protocol (User Datagram Protocol, UDP), Gigabit Ethernet Vision Control Protocol (GigE Vision Control Protocol, GVCP), Gigabit Ethernet Vision Data stream protocol (GigE Vision Stream Protocol, GVSP) package and analysis IP core, and use the parallel processing of FPGA to transmit image data to the host computer for real-time display according to the requirements of Gige Vision protocol.

[0052] An FPGA-based Gige Vision interface image transmission system, including a CMOS image sensor, a PC host computer, a local Gigabit Ethernet network, and an embedded image acquisition device based on a Gige interface, wherein the embedded...

Embodiment 2

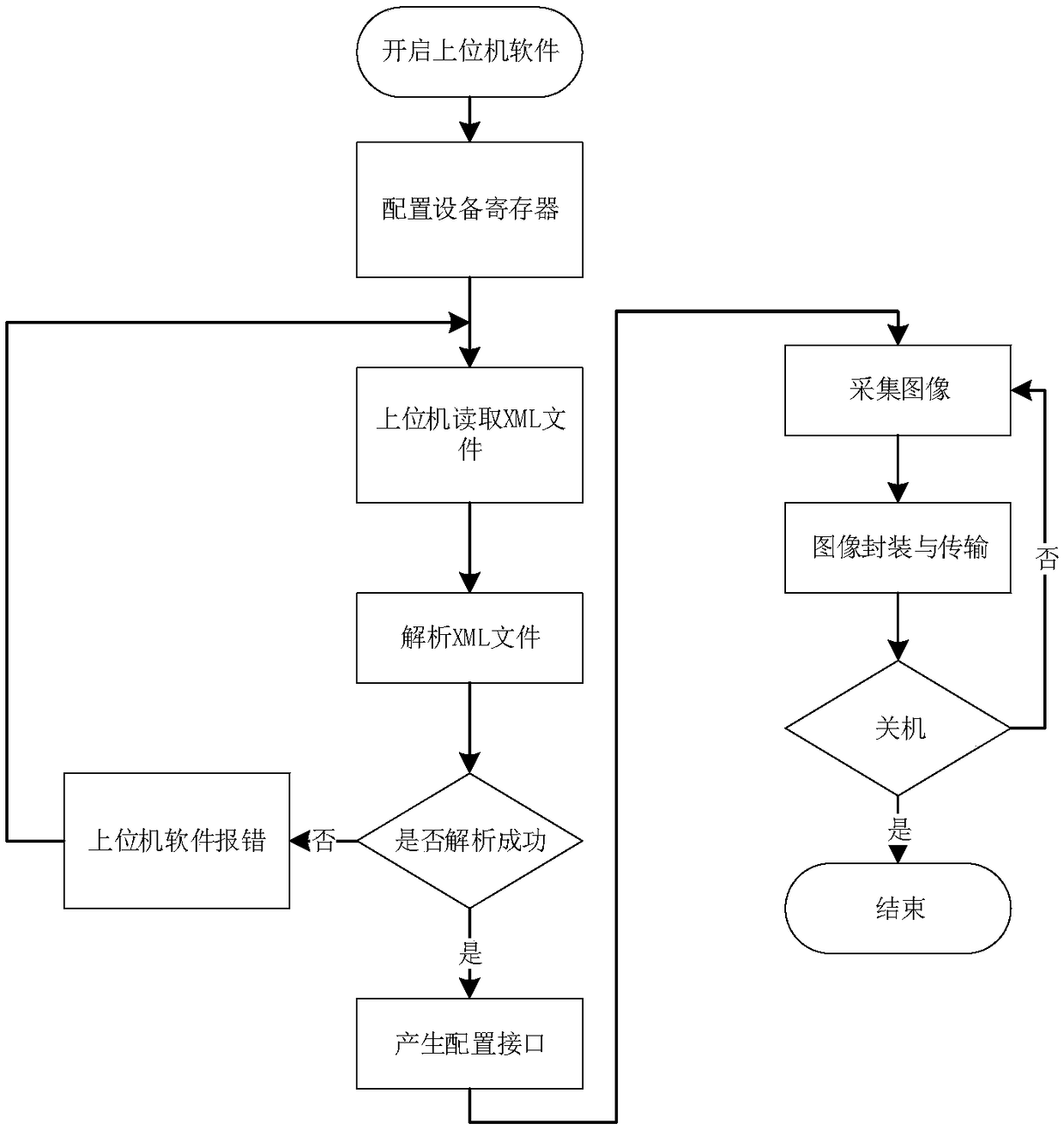

[0072] refer to figure 1 , an FPGA-based Gige Vision interface image transmission implementation method, the overall operation process is:

[0073] a) The camera, embedded image acquisition device and computer are connected to the same local area network, and the system is powered on and initialized;

[0074] b) The upper computer sends the signaling message GVCP, and performs information interaction with the FPGA through the Gigabit Ethernet interface, and negotiates and configures the general boot register and user register in the device;

[0075] c) After the upper computer completes the basic device read and write register operations, it reads the device XML description file in the form of a signaling message;

[0076] d) The host computer software automatically parses the XML file, if the parsing is successful, proceed to the next step, otherwise the software reports an error and returns to step c);

[0077] e) The host computer generates configuration interfaces and tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com