Piezoelectric MEMS acceleration sensor and a preparation method thereof

An acceleration sensor and piezoelectric technology, applied in the field of micro sensors, can solve the problems of poor anti-overload capacity and low resonance frequency, and achieve the goal of increasing the bending stiffness, improving the quality factor, and improving the reliability and stability of the detection results. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

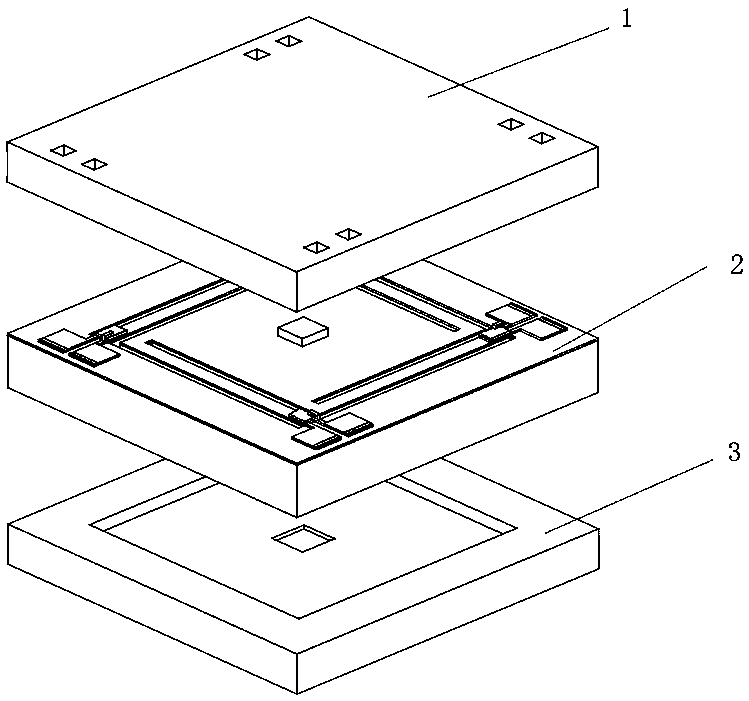

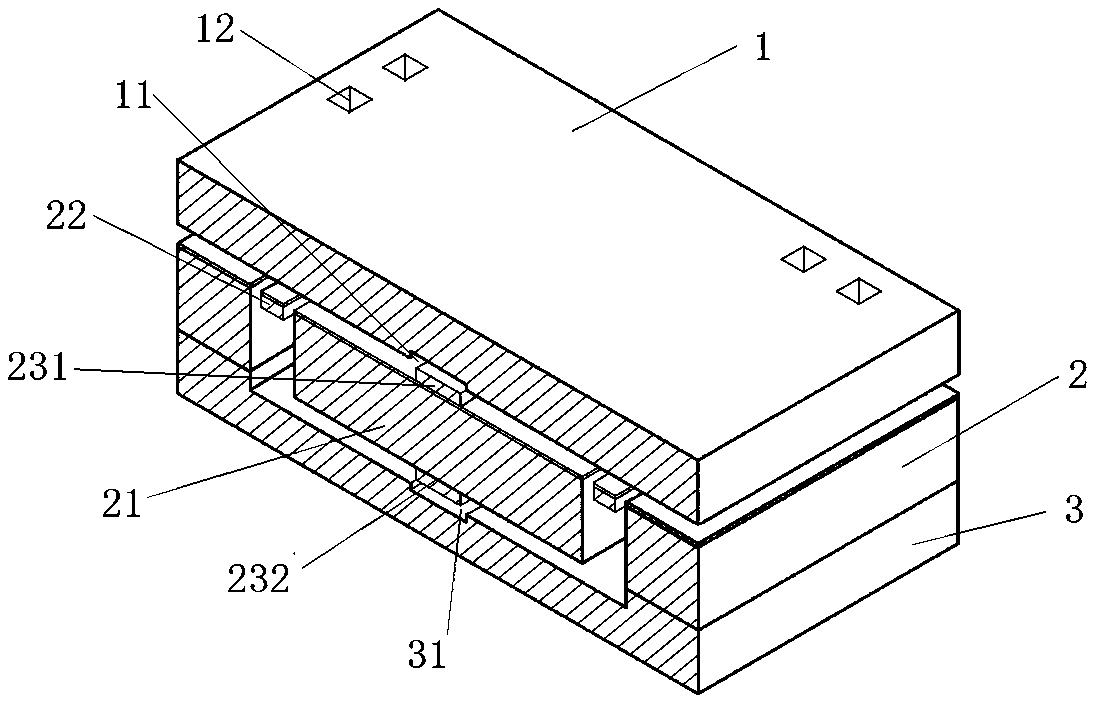

[0065] see figure 1 , figure 2 , the present embodiment provides a piezoelectric MEMS acceleration sensor, which is composed of a cover plate 1, a detection structure layer 2 and a substrate 3 connected in sequence;

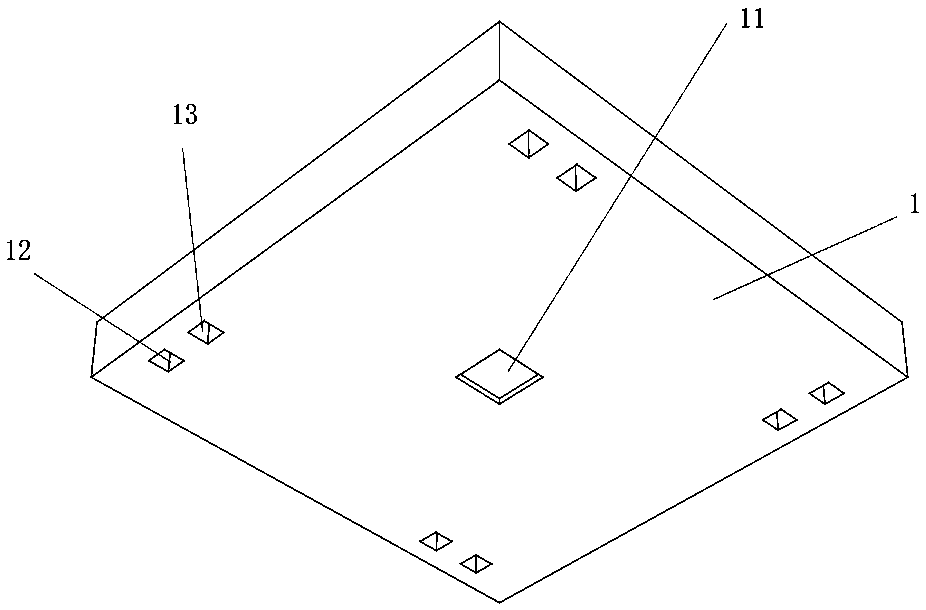

[0066] like image 3 As shown, the cover plate 1 is made on the basis of the crystal orientation N-type single-polished silicon wafer. The center of the bottom surface of the cover plate 1 is provided with an upper limit groove 11, and the four corners of the top surface of the cover plate 1 are respectively Two wire lead-out holes 12 are provided, and the wire lead-out holes 12 are set through the cover plate 1 .

[0067] like Figure 4-6 As shown, the detection structure layer 2 is made on the basis of a square double-thrown SOI silicon wafer. The detection structure layer 2 includes a square outer frame 24, a sensitive mass 21 and four L-shaped fixed beams 22 arranged in the outer frame 24, and the sensitive The outer periphery of the mass block 21 is re...

Embodiment 2

[0072] This embodiment provides a preparation method of a piezoelectric MEMS acceleration sensor, the operation steps are as follows:

[0073] Preparation: Take a double-throw SOI silicon wafer with a thickness of 351 μm and two single-throw N-type silicon wafers with crystal orientation with a thickness of 300 μm;

[0074] One-time photolithography: use the standard semiconductor cleaning process to clean the double-polished SOI silicon wafer, and place the cleaned double-polished SOI silicon wafer in an etching tank containing potassium hydroxide solution for thinning treatment, and the overall thickness of the substrate layer is reduced to 50 μm. The photoresist is spin-coated at the center of the surface of the substrate layer, developed by photolithography, and then the lower limit post 232 with a side length of 30 μm and a height of 8 μm is etched using an ICP etching (inductively coupled plasma) process, as shown in Figure 8 shown;

[0075] Secondary photolithography...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More