Ultrathin silicon nitride micro-gate chip

A technology of silicon nitride micro-gate and silicon nitride layer, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., and can solve problems such as large background noise of copper grid, large background noise, and difficult atomic-level imaging , to achieve the effects of overcoming image damage, high image signal-to-noise ratio, and wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

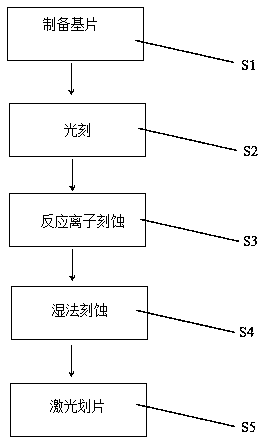

[0029] S1) Preparation of the substrate: Prepare a silicon substrate with silicon nitride layers on both sides, the size of the silicon substrate is 3mm*3mm, the thickness is 100μm, and the thickness of the silicon nitride layer is 5nm;

[0030] S2) Lithography: Expose in a UV lithography machine for 15 seconds, transfer the square porous window pattern from the photolithography mask to the side of the silicon substrate of S1), then place the silicon substrate in a positive gel developer for 30 seconds, and then Clean the surface with deionized water;

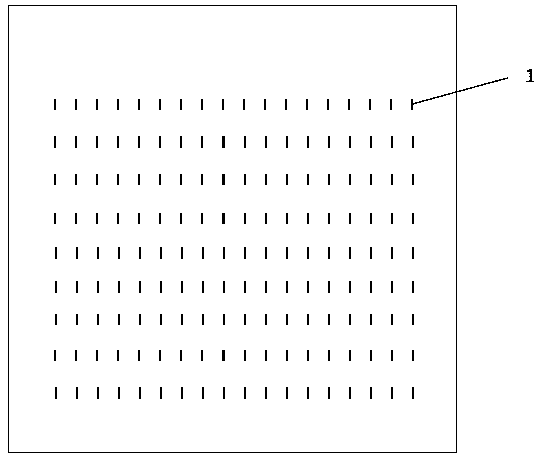

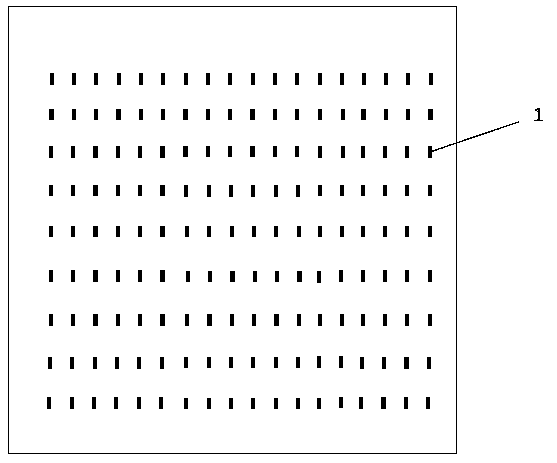

[0031] S3) Reactive ion etching: multiple viewing windows 1 are etched on the silicon nitride layer on the other side of the silicon substrate produced in S2). The viewing window 1 is 5μm*50μm in size, and then the silicon substrate is placed Into SF 6 Soak in medium for 90 seconds, with window 1 facing upward, and finally use SF 6 Rinse, wash away the photoresist;

[0032] S4) Wet etching: Put the silicon substrate produced in S3) i...

Embodiment 2

[0035] S1) Preparation of the substrate: prepare a silicon substrate with silicon nitride layers on both sides, the size of the silicon substrate is 3mm*3mm, the thickness is 100μm, and the thickness of the silicon nitride layer is 25nm;

[0036] S2) Photolithography: Expose in a UV lithography machine for 18s, transfer the square porous window pattern from the photolithography mask to the side of the silicon substrate of S1), then place the silicon substrate in a positive rubber developer for 40s, and then Clean the surface with deionized water;

[0037] S3) Reactive ion etching: multiple viewing windows 1 are etched on the silicon nitride layer on the other side of the silicon substrate produced in S2). The viewing window 1 is 15μm*50μm in size, and then the silicon substrate is placed Enter CHF 3 O 2 Soak in medium for 100s, with window 1 facing up, and finally use CHF 3 O 2 Rinse, wash away the photoresist;

[0038] S4) Wet etching, put the silicon substrate produced in S3) into...

Embodiment 3

[0041] S1) Preparation of the substrate: prepare a silicon substrate with silicon nitride layers on both sides, the size of the silicon substrate is 3mm*3mm, the thickness is 100μm, and the thickness of the silicon nitride layer is 50nm;

[0042] S2) Lithography: Expose in a UV lithography machine for 23 seconds, transfer the square porous window pattern from the photolithography mask to the side of the silicon substrate of S1), then place the silicon substrate in a positive rubber developer for 50 seconds, and then Clean the surface with deionized water;

[0043] S3) Reactive ion etching: multiple viewing windows 1 are etched on the silicon nitride layer on the back of the silicon substrate produced in S2). The viewing window 1 is 30μm*50μm in size, and then the silicon substrate is placed SF 6 Soak in medium for 110s, with window 1 facing up, and finally use SF 6 Rinse, wash away the photoresist;

[0044] S4) Wet etching: Put the silicon substrate produced in S3) into a 9.8mol / L p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More