Silicon wafer packaging structure and preparation method thereof

A technology of packaging structure and silicon wafer, which is used in semiconductor/solid-state device manufacturing, electrical components, and electrical solid-state devices. /O pitch, large bump area, effect of increasing reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

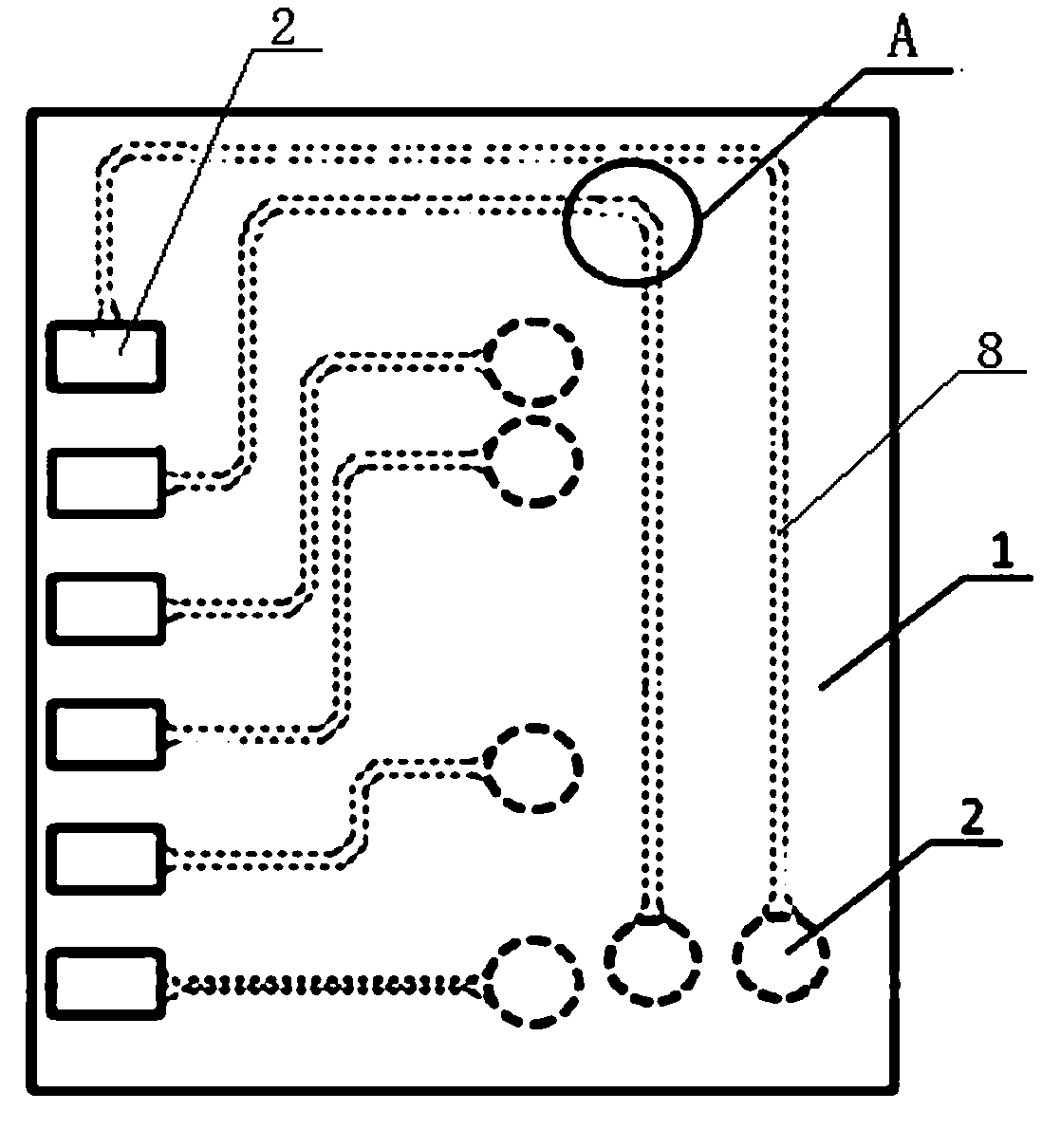

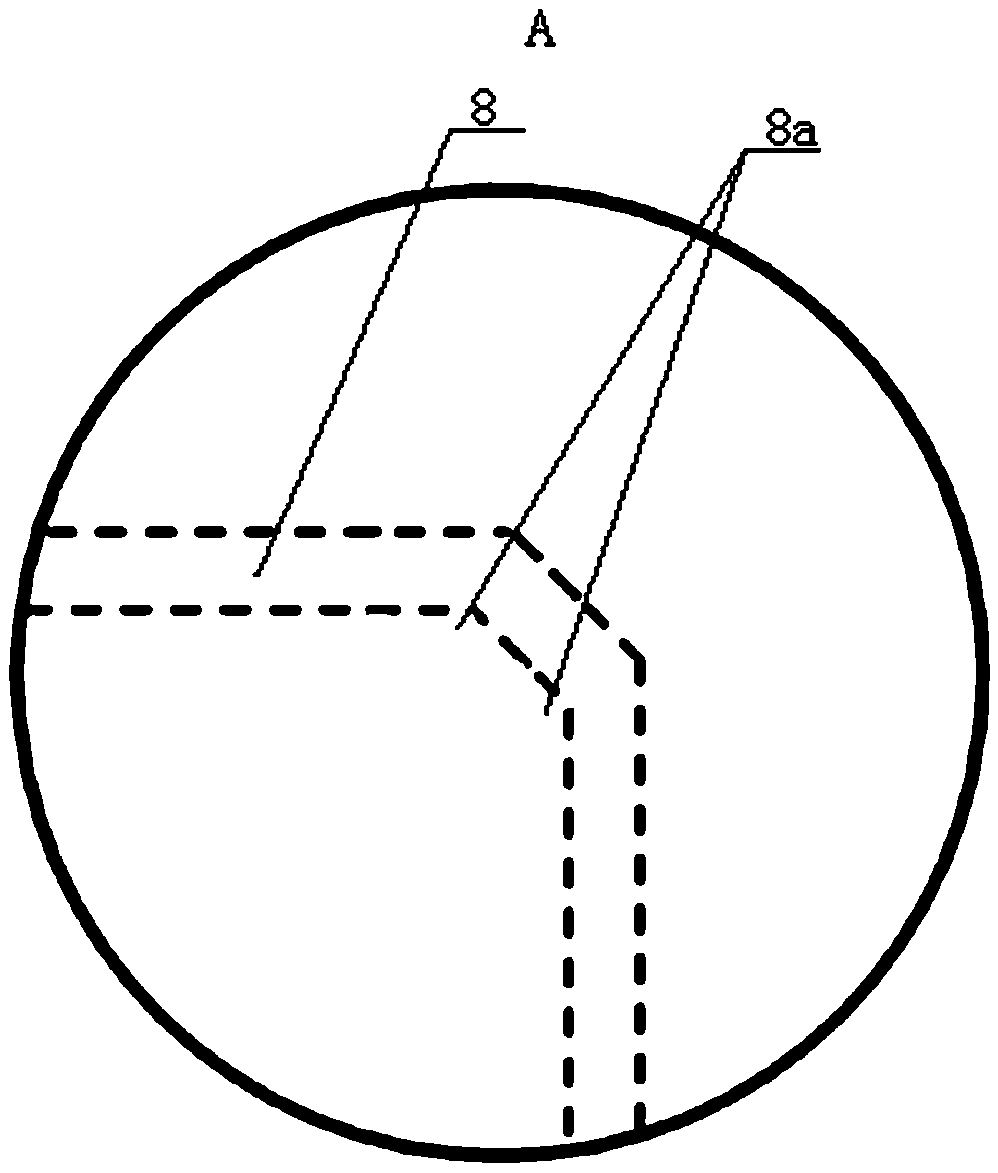

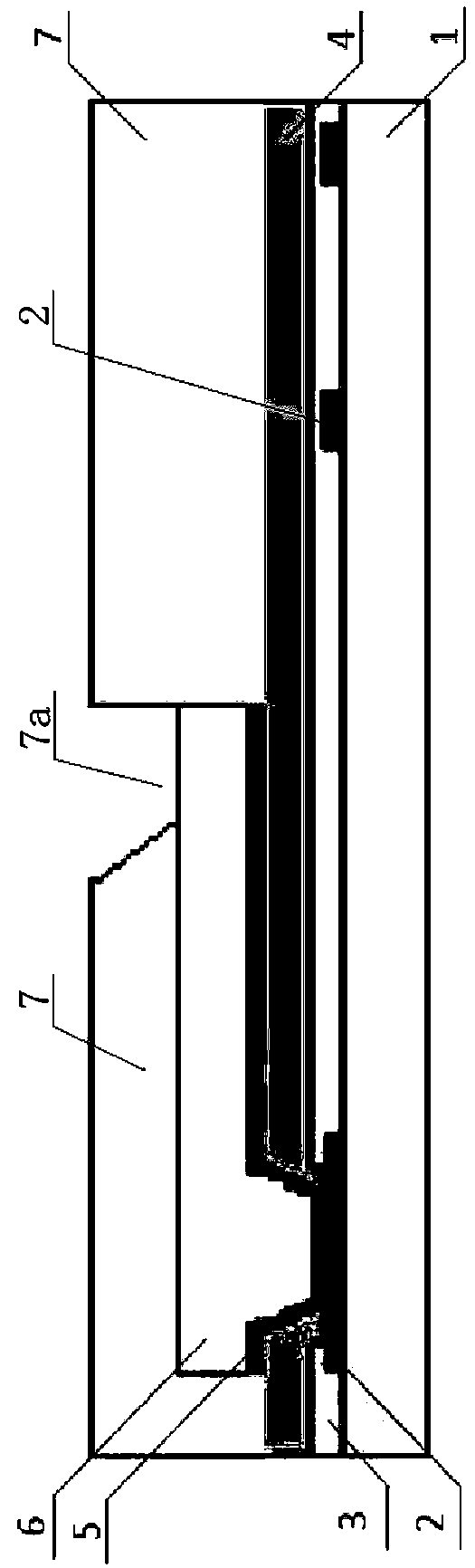

[0039] like Figure 1-13 As shown, it is a silicon chip packaging structure, including a silicon chip 1, a number of aluminum pads 2 are distributed on the surface of the silicon chip 1, and a silicon chip protective layer 3 is also covered on the silicon chip 1 and the aluminum pad 2. The thickness of the layer 3 is greater than the thickness of the aluminum pad 2, and a number of aluminum pad grooves 2a are provided on the silicon wafer protection layer 3 corresponding to each aluminum pad 2. It is also covered with a first insulating protective layer 4 made of polyimide. The lower side of the first insulating protective layer 4 is integrally provided with a lower protrusion 4a embedded in the aluminum pad groove 2a. The first insulating protective layer 4 is located on the lower side. A window slot 4b is provided above the protrusion 4a, and the window slot 4b is located above the aluminum pad 2, and an adhesive conductive layer 5 is provided above the first insulating prot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More