Preparation method of semiconductor structure

A semiconductor and silicon-on-insulator technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problem of uncertain channel current and other problems, and improve the electrical stability of the device and the channel current. Stabilizes and prevents oxidation and wear and tear

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0032] The invention provides a method for preparing a semiconductor structure, which includes: providing a semiconductor substrate, an oxide layer is formed on at least a first part of the surface of the semiconductor substrate, and a photoresist layer is formed on at least a second part of the surface; removing a partial thickness of the oxide layer by etching to leave a predetermined thickness of residual oxide layer; and removing the photoresist layer by dry etching.

[0033] Description is made below with reference to the accompanying drawings.

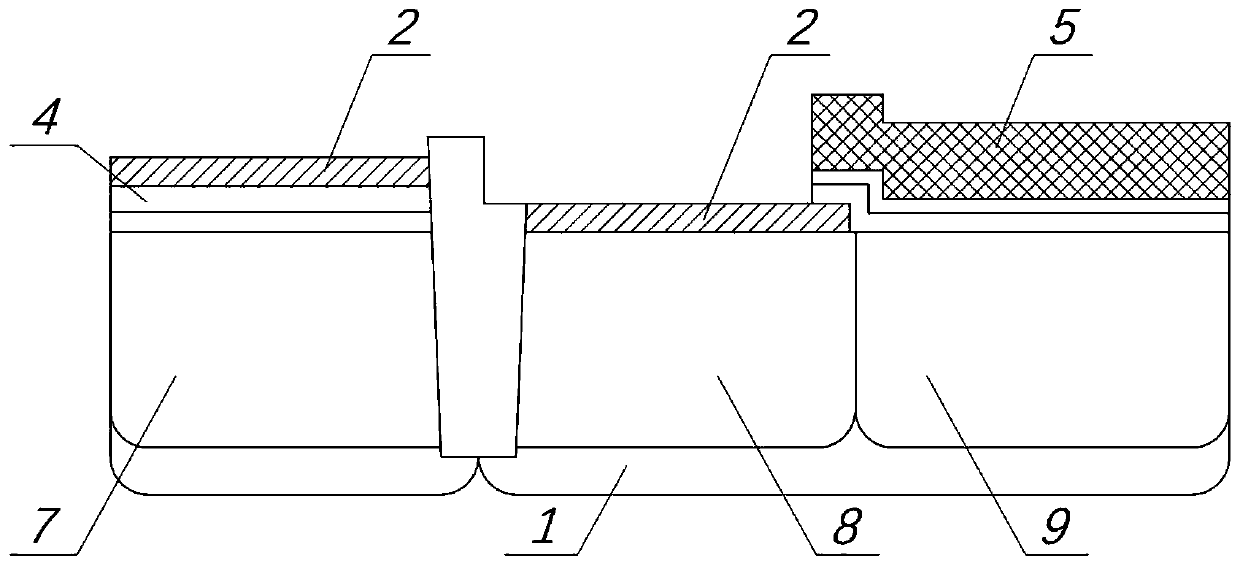

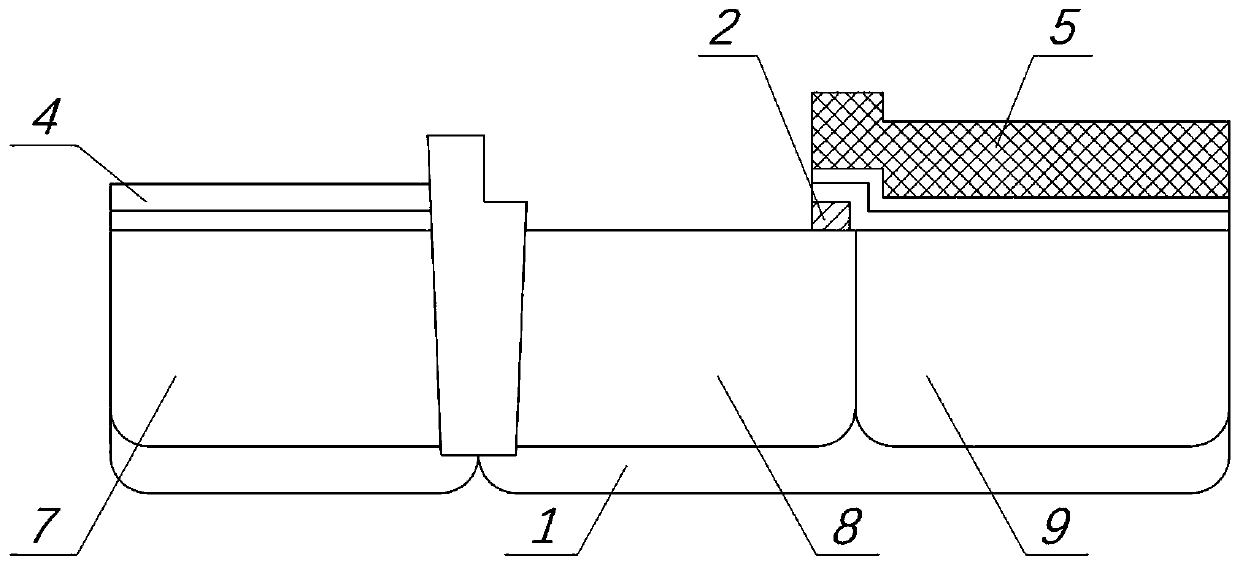

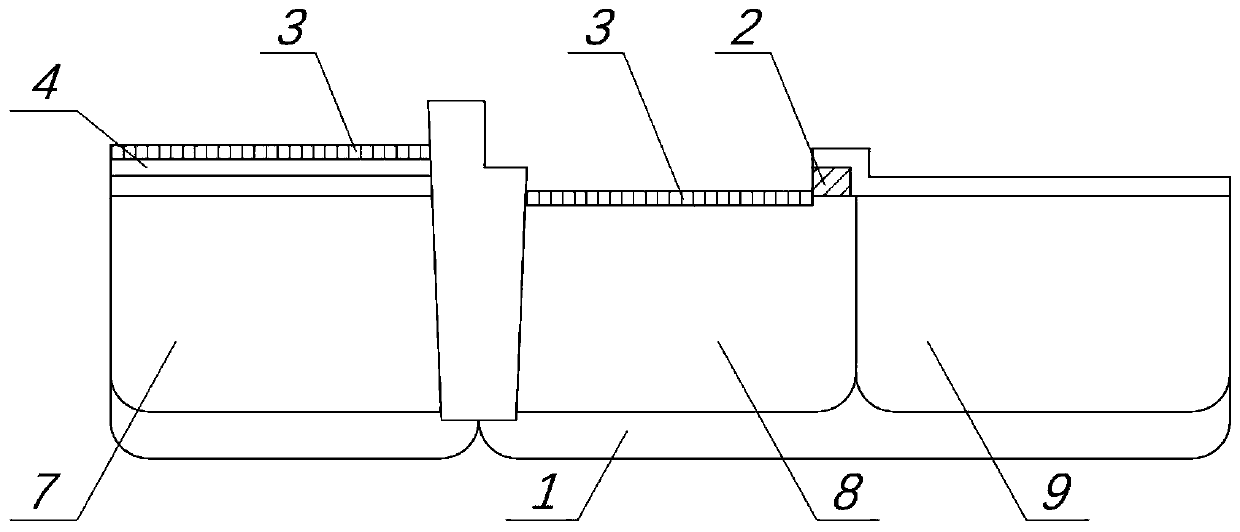

[0034] Please refer to Figure 1 to Figure 3 ,in, figure 1 It is a schematic diagram before wet etching in the process flow of a SONOS flash memory device. figure 2 It is a schematic diagram after wet etching in the process flow of a SONOS flash storage device. image 3 It is a schematic diagram of a SONOS flash storage device process after dry etching and adhesive removal.

[0035] Such as Figure 1 to Figure 3 As shown, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com