Low-power-consumption ultra-high-speed high-precision analog-to-digital converter

An analog-to-digital converter, ultra-high-speed technology, applied in the direction of analog-to-digital converter, analog/digital conversion, analog/digital conversion calibration/test, etc., to achieve the effect of avoiding power consumption, eliminating influence, and shortening output time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

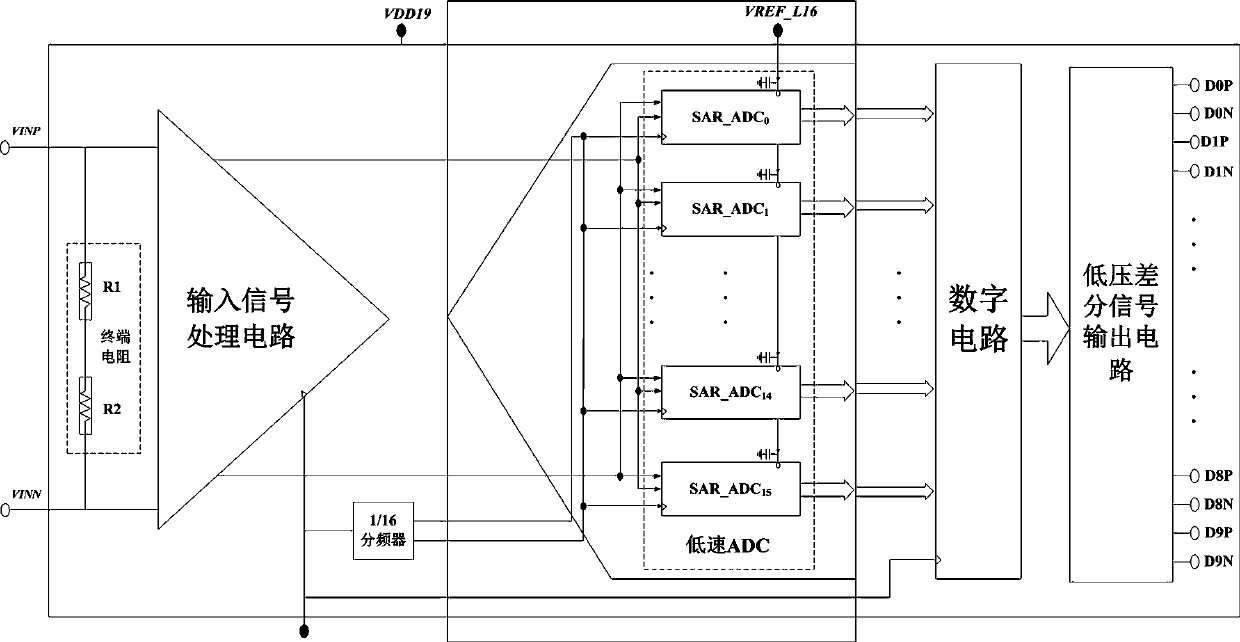

[0039] The present invention designs a low-power ultra-high-speed high-precision analog-to-digital converter, which is a low-power ADC circuit architecture with a 10-bit resolution gigahertz sampling frequency built in an IC chip, such as figure 1 , figure 2As shown, the following configuration structure is adopted in particular: including input circuit, low-speed ADC, 1 / 16 frequency divider and output circuit, the input circuit is connected to the low-speed ADC, the low-speed ADC is connected to the output circuit, and the 1 / 16 frequency divider is respectively It is connected with the input circuit and the low-speed ADC; the input circuit samples the input signal at a frequency of 1.6GHz; the low-speed ADC acquires the signal from the input circuit at a frequency of 100MHz.

[0040] As a preferred setting scheme, the low-power ultra-high-speed high-precision analog-to-digital converter is mainly composed of four major parts: an input circuit, a low-speed ADC, a 1 / 16 frequen...

Embodiment 2

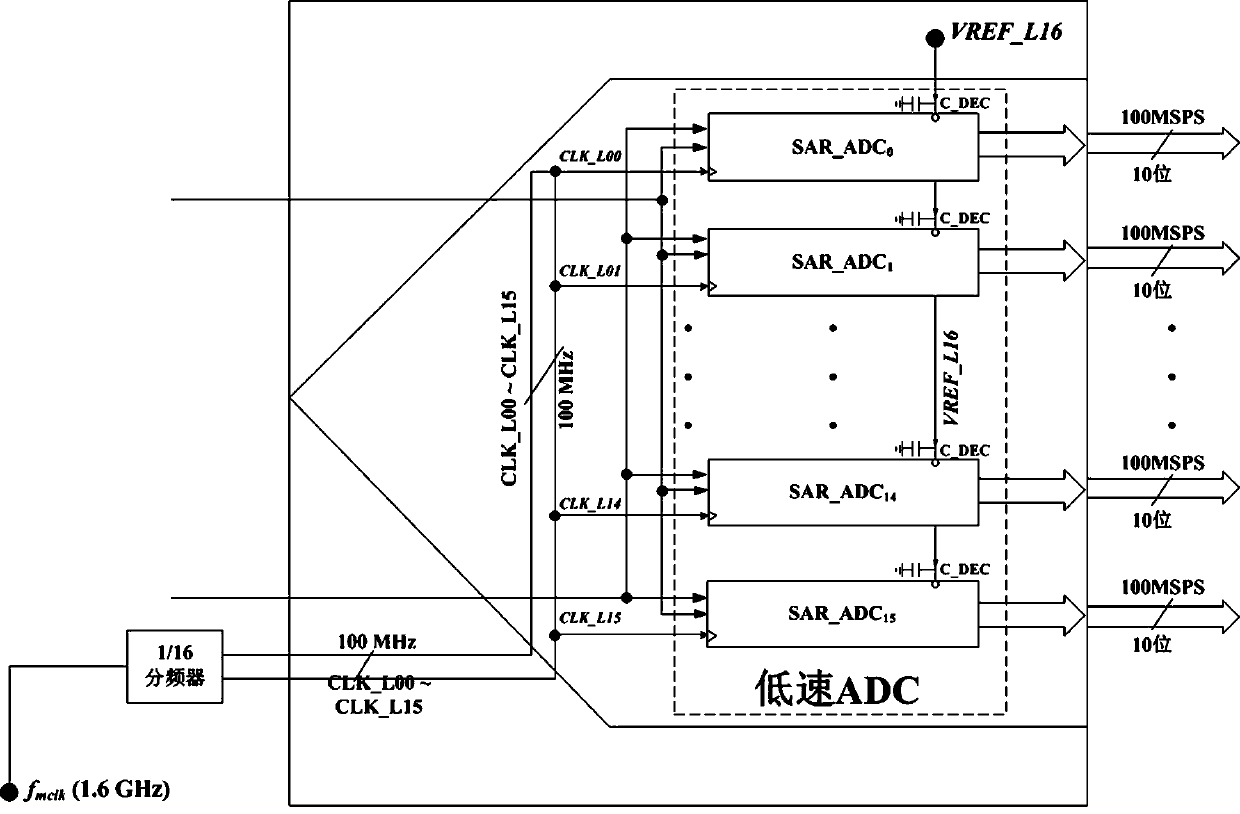

[0042] This embodiment is further optimized on the basis of the foregoing embodiments, and the same parts as the technical solutions of the preceding embodiments will not be repeated here, such as figure 1 , figure 2 As shown, further in order to better realize the present invention, the following setting method is adopted in particular: the low-speed ADC includes 16 SAR_ADCs that work in time-division and alternate sampling, the SAR_ADCs are all connected in parallel with the input circuit, and the 1 / 16 frequency divider is controlled and connected SAR_ADC, SAR_ADC is connected with the output circuit.

[0043] As a preferred setting scheme, the low-speed ADC is mainly composed of 16 SAR_ADCs that work in time-division alternate sampling. The 16 SAR_ADCs that work in time-division alternate The SAR_ADC with alternate sampling work is connected, and the 1 / 16 frequency divider controls the connection of 16 SAR_ADC with time-division alternate sampling work, and the 16 SAR_ADC...

Embodiment 3

[0045] This embodiment is further optimized on the basis of any of the above-mentioned embodiments, and the same parts as the technical solutions of the foregoing embodiments will not be repeated here, such as figure 1 , figure 2 As shown, further in order to better realize the present invention, the following setting method is adopted in particular: a local capacitance is arranged at any reference voltage access point of SAR_ADC, as a preferred setting scheme, at the reference voltage connection point of each SAR_ADC The input point introduces a local capacitor (C_DEC) to reduce the dynamic mismatch between reference voltages, thereby greatly reducing the gain mismatch between SAR_ADC and improving the performance of ultra-high-speed and high-precision analog-to-digital converters.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More