Tunneling field effect transistor and forming method thereof

A tunneling field effect, transistor technology, applied in the manufacturing of diodes, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of poor driving ability, low threshold slope, low operating voltage, etc., to achieve good conductivity and reduce contact resistance. , the effect of increasing the current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As mentioned in the background, the performance of prior art tunneling field effect transistors is poor.

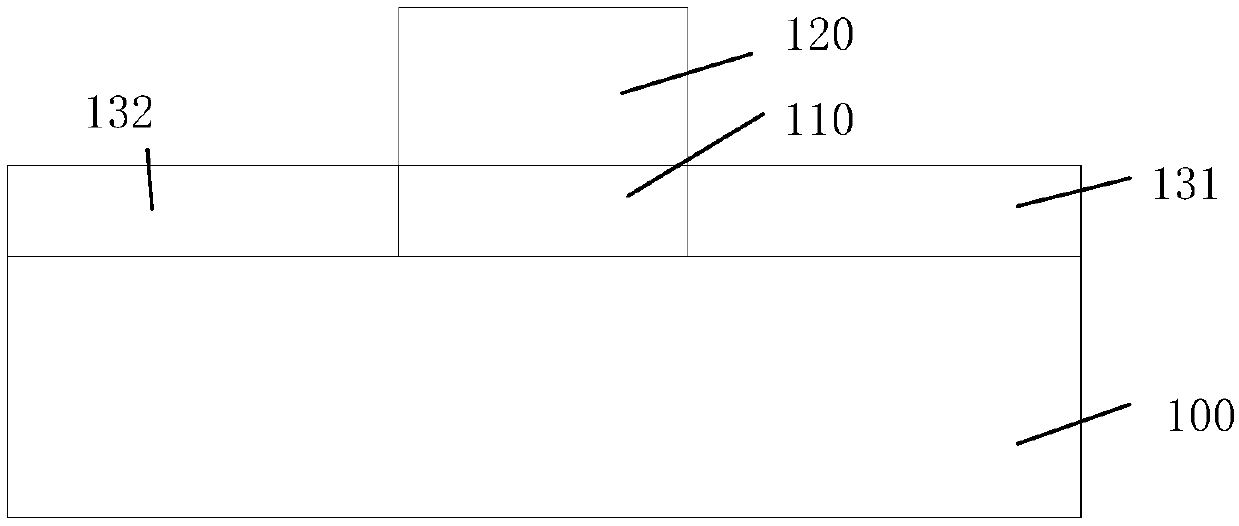

[0032] figure 1 It is a schematic diagram of the structure of a tunneling field effect transistor.

[0033] A tunneling field effect transistor, reference figure 1 , comprising: a semiconductor substrate 100, a channel region 110 located on the surface of the semiconductor substrate 100, a gate structure 120 located on the surface of the channel region, and a third doped region in the semiconductor substrate 100 located on both sides of the gate structure 120 131 and the fourth doped region 132.

[0034]The third doped region 131 and the fourth doped region 132 are respectively the source end and the drain end of the tunneling field effect transistor, one of which is a P region (hole doping), and the other is an N region (electron doping). ), the middle channel region 110 is an intrinsic material. Under the driving voltage, holes can tunnel from the P region to...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More