Chip and antenna integrated three-dimensional packaging structure and preparation method thereof

A three-dimensional packaging and chip technology, which is applied in the structural form of radiation elements, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of large packaging volume, poor integration, and large loss, and achieve high integration performance, low cost, and low loss. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

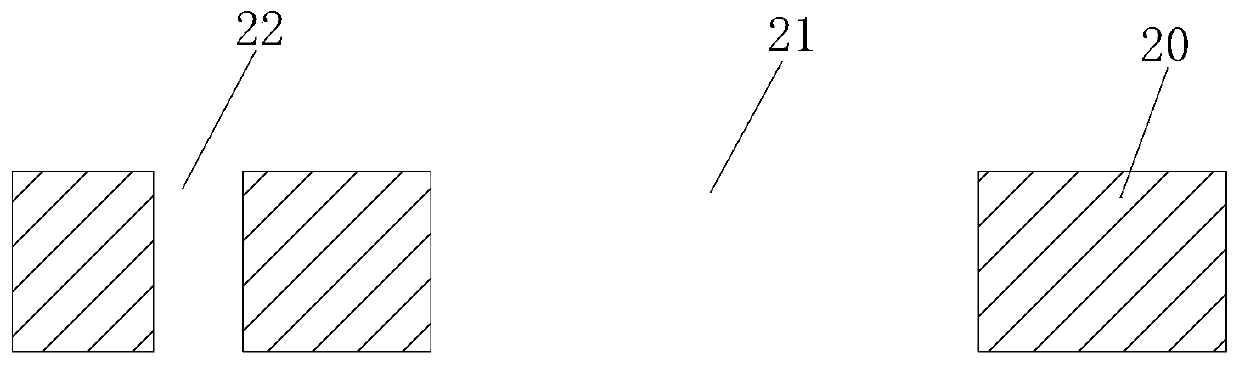

[0043] see figure 1 , a chip and antenna integrated three-dimensional packaging structure, including at least one chip 10 and a glass substrate 20 . The chip 10 has a first surface and a second surface, the first surface is provided with functional areas and electrodes 11, and the second surface is opposite to the first surface. The chip 10 of the present invention is mainly a millimeter-wave chip, which includes gallium arsenide (GaAs), InP (indium phosphide) millimeter-wave chips, gallium nitride (GaN) millimeter-wave chips, and the like.

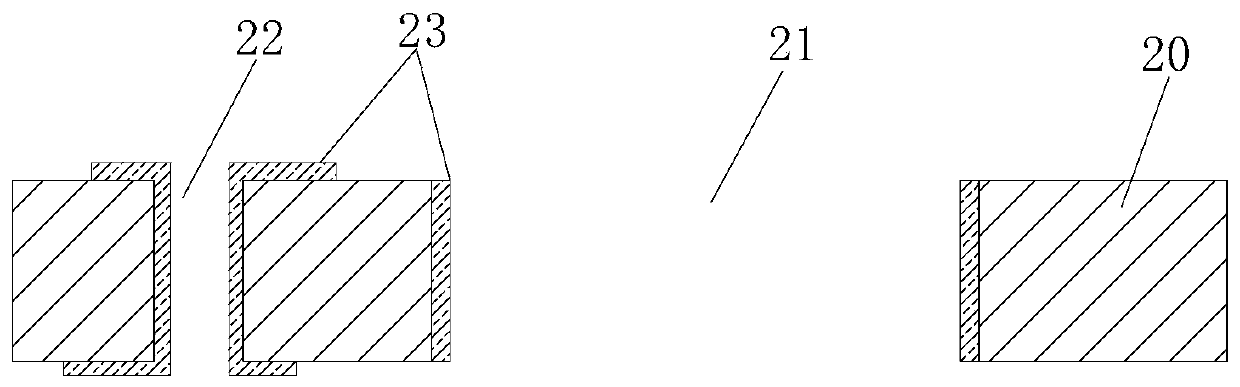

[0044] At least one through groove 21 and at least one through hole 22 are arranged on the glass substrate 20, and there is a distance between the through groove 21 and the through hole 22. The number of through grooves 21 can be one, two or even more, and the number of through holes 22 The quantity can be one, two, three or even more.

[0045] Metal conductive material 23 is deposited on the inner wall of the through groove 21 and the ...

Embodiment 2

[0063] see Figure 8 , a chip and antenna integrated three-dimensional packaging structure and its preparation method, its main features are the same as the first embodiment, the difference is that no passivation layer is provided on the surface of the antenna layer 53 and the exposed surface of the insulating layer 54. In the corresponding preparation method, the step of forming a passivation layer on the surface of the antenna layer 53 and the exposed surface of the insulating layer 54 is not included.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More