Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems such as repeated erasing times index is not up to standard, so as to improve the speed and performance of the device and increase the conduction current , The effect of saving process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

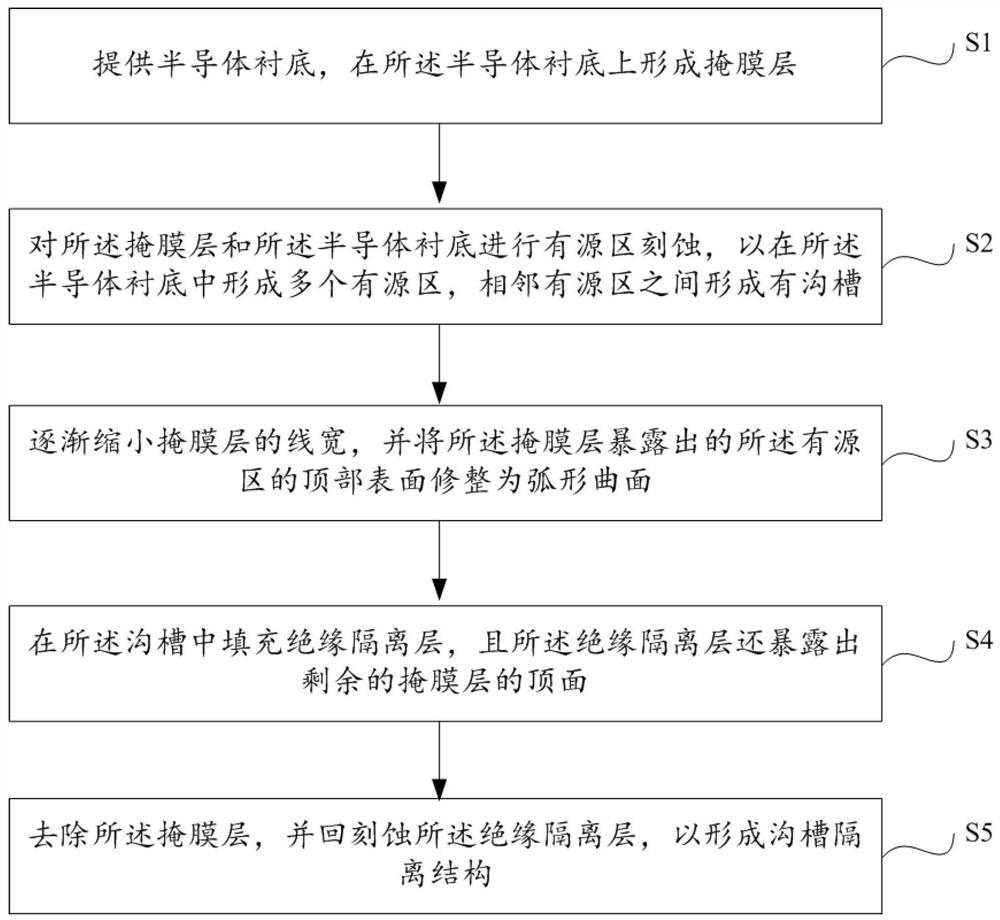

Method used

Image

Examples

Embodiment Construction

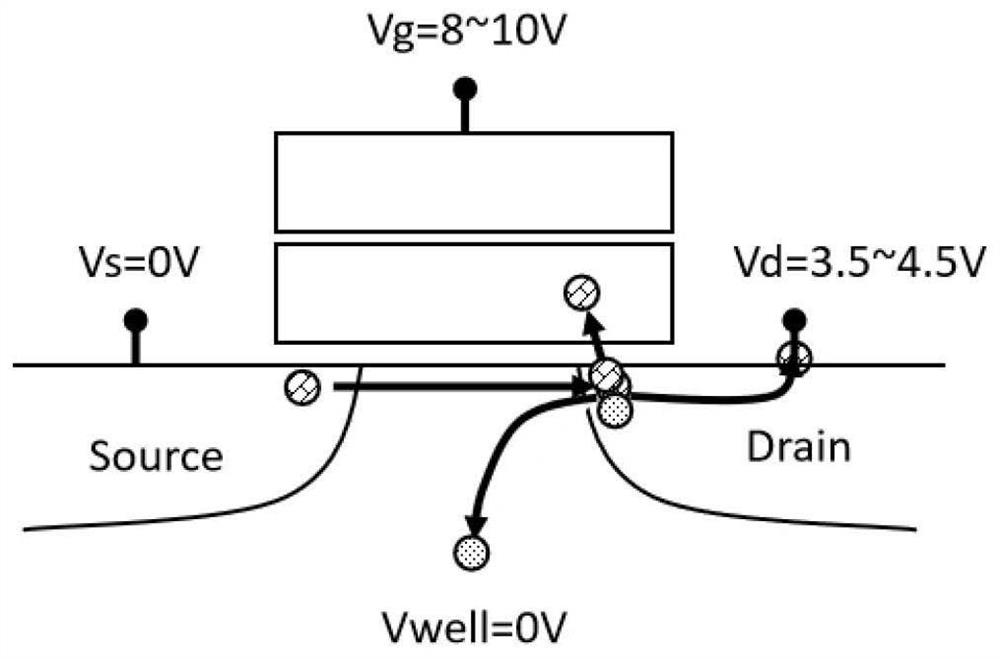

[0045] Transistor conduction current principle:

[0046]

[0047] In the formula, Idsat is the conduction current, Cox is the parasitic capacitance, μ is a constant, W is the effective channel width, L is the effective channel length, V GS is the gate-source voltage difference, VT is the threshold voltage.

[0048] It can be seen from the above formula that the conduction current Idsat of the transistor is inversely proportional to the effective channel length L and directly proportional to the effective channel width W.

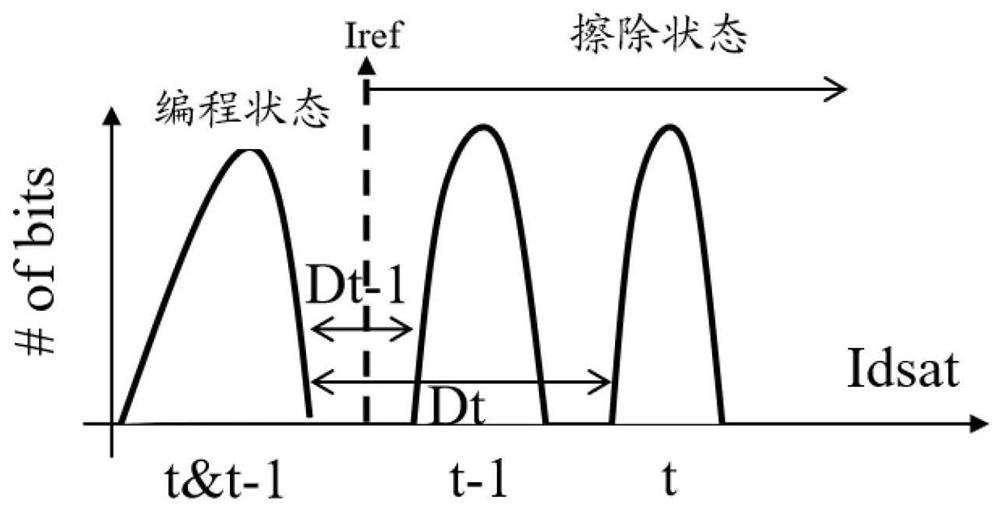

[0049] As mentioned in the background art, the logic circuit has evolved all the way to the current 5nm process, which is mainly to reduce the effective channel length L of the MOS transistor and increase the speed of the logic circuit.

[0050] However, the conduction current Idsat of the transistor is also proportional to the effective channel width W, so the conduction current can be increased by increasing the effective channel width W at this time. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More