Cellular structure of silicon carbide device, preparation method of cellular structure and silicon carbide device

A silicon carbide and silicon carbide substrate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as deterioration, device failure reliability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

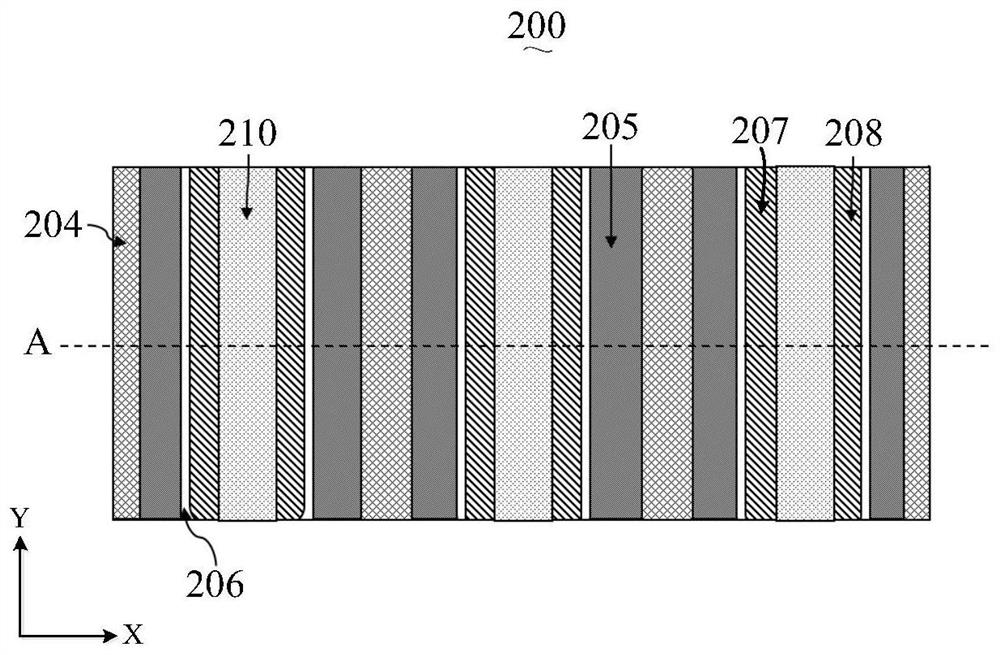

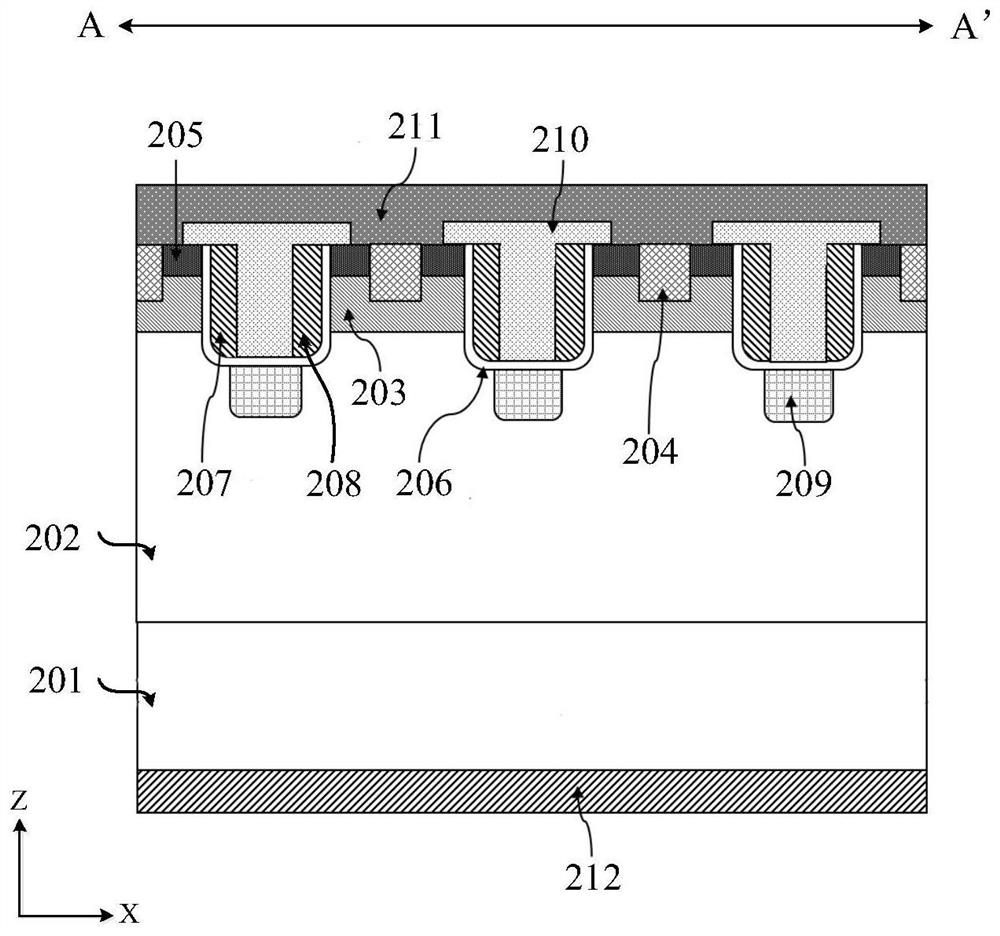

[0102] Such as figure 2 and image 3As shown, the embodiment of the present disclosure provides a cell structure 200 of a silicon carbide device, including a substrate 201, a drift layer 202, a well region 203, a first source region 204, a second source region 205, a first gate trench (not marked in the figure), gate oxide layer 206 , first gate 207 , second gate 208 , first shielding region 209 , interlayer dielectric layer 210 , source metal layer 211 and drain metal layer 212 .

[0103] It should be noted that, in order to figure 2 Clearly show the first source region 204, the second source region 205, the first gate trench (not marked in the figure), the gate oxide layer 206, the first gate 207, the second gate 208 and the interlayer dielectric layer 210 shape and position, so figure 2 The substrate 201, the drift layer 202, the well region 203, the first shielding region 209, the source metal layer 211 and the drain metal layer 212, as well as the first gate 207 and...

Embodiment 2

[0120] Such as Figure 4 and Figure 5 As shown, the embodiment of the present disclosure provides another cell structure 300 of a silicon carbide device, including a substrate 301, a drift layer 302, a well region 303, a first source region 304, a second source region 305, a first gate trench Groove (not marked in the figure), second gate trench (not marked in the figure), first shielding area 306, second shielding area 307, gate oxide layer 308, first gate 309, second gate 310 , a third gate 311 , a fourth gate 312 , an interlayer dielectric layer 313 , a source metal layer 314 and a drain metal layer 315 .

[0121] It should be noted that, in order to Figure 4 Clearly show the first source region 304, the second source region 305, the first gate trench (not marked in the figure), the second gate trench (not marked in the figure), the gate oxide layer 308, the first gate 309, the shapes and positions of the second gate 310, the third gate 311, the fourth gate 312 and the...

Embodiment 3

[0140] On the basis of the first embodiment, this embodiment provides a method for preparing a cell structure 200 of a silicon carbide device. Figure 6 It is a schematic flowchart of a method for preparing a cell structure 200 of a silicon carbide device shown in an embodiment of the present disclosure. Figure 7-Figure 13 It is a schematic cross-sectional structure formed by related steps of a method for manufacturing a silicon carbide device cell structure 200 shown in an embodiment of the present disclosure. Below, refer to Figure 6 and Figure 7-Figure 13 The detailed steps of an exemplary method of the method for manufacturing the cell structure 200 of the silicon carbide device proposed by the embodiment of the present disclosure will be described.

[0141] Such as Figure 6 As shown, the method for preparing the cellular structure 200 of the silicon carbide device in this embodiment includes the following steps:

[0142] Step S201: if Figure 7 As shown, a silico...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More