Cellular structure of silicon carbide device, preparation method thereof and silicon carbide device

A silicon carbide and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as variation, device failure reliability, etc., and achieve low manufacturing cost, which is conducive to current sharing and manufacturability strong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

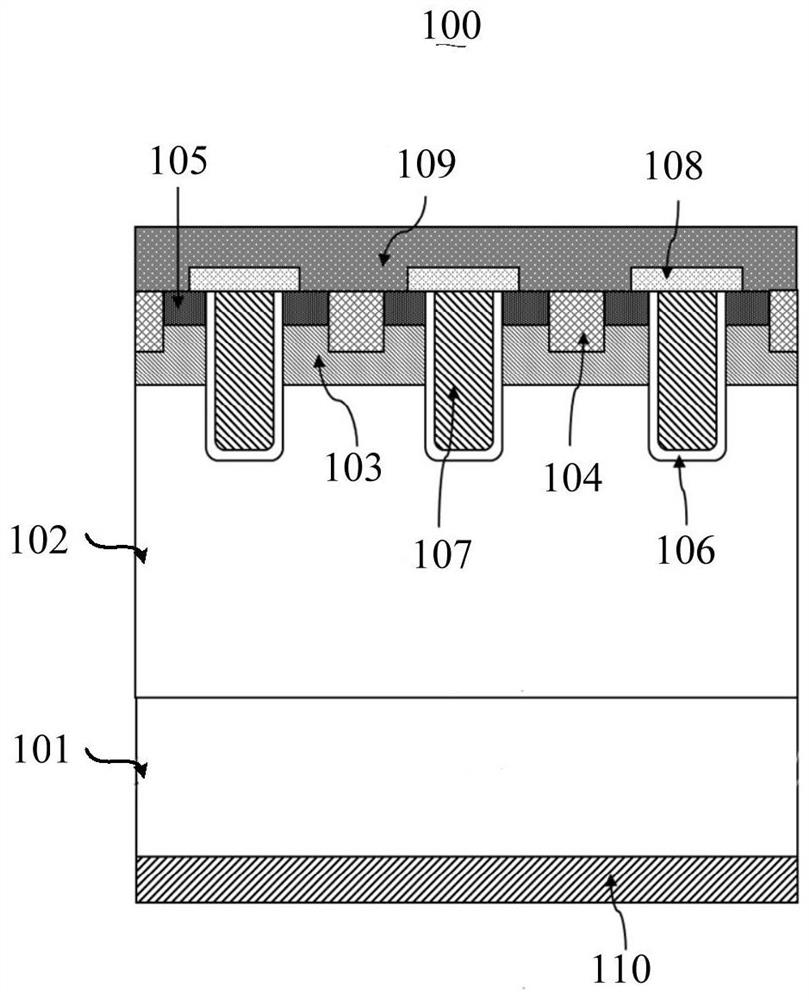

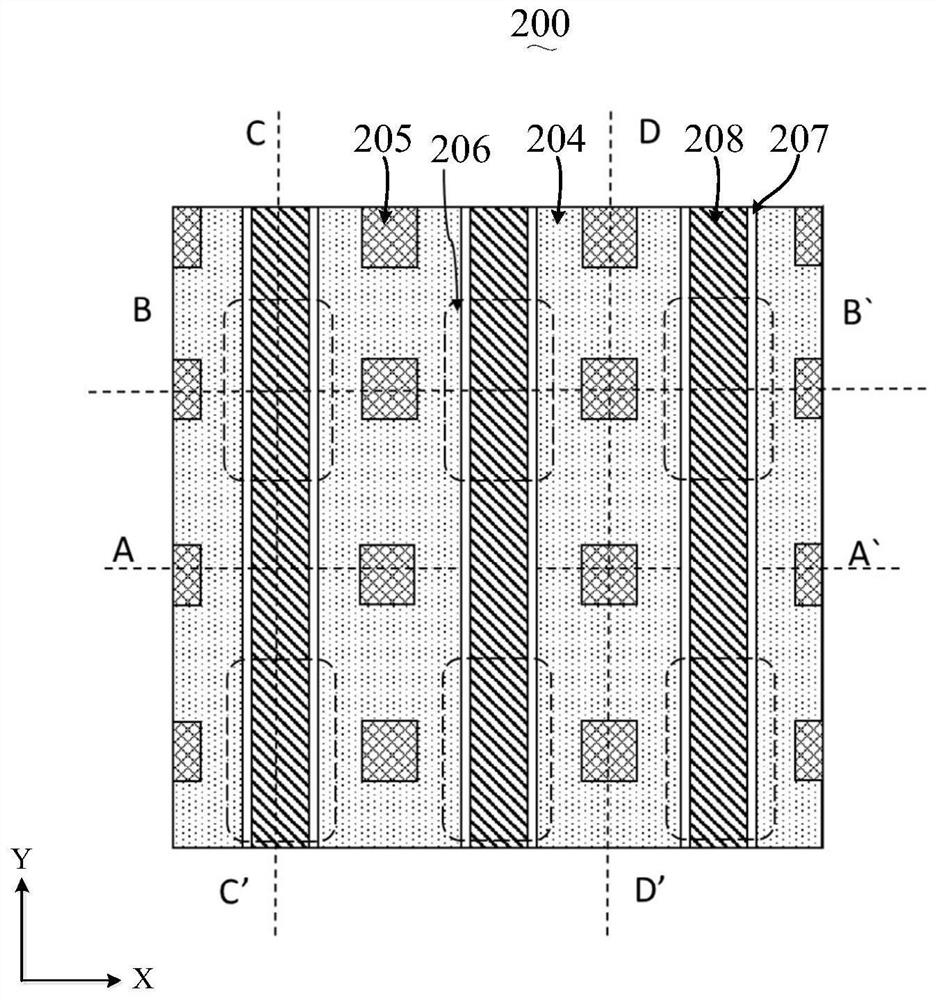

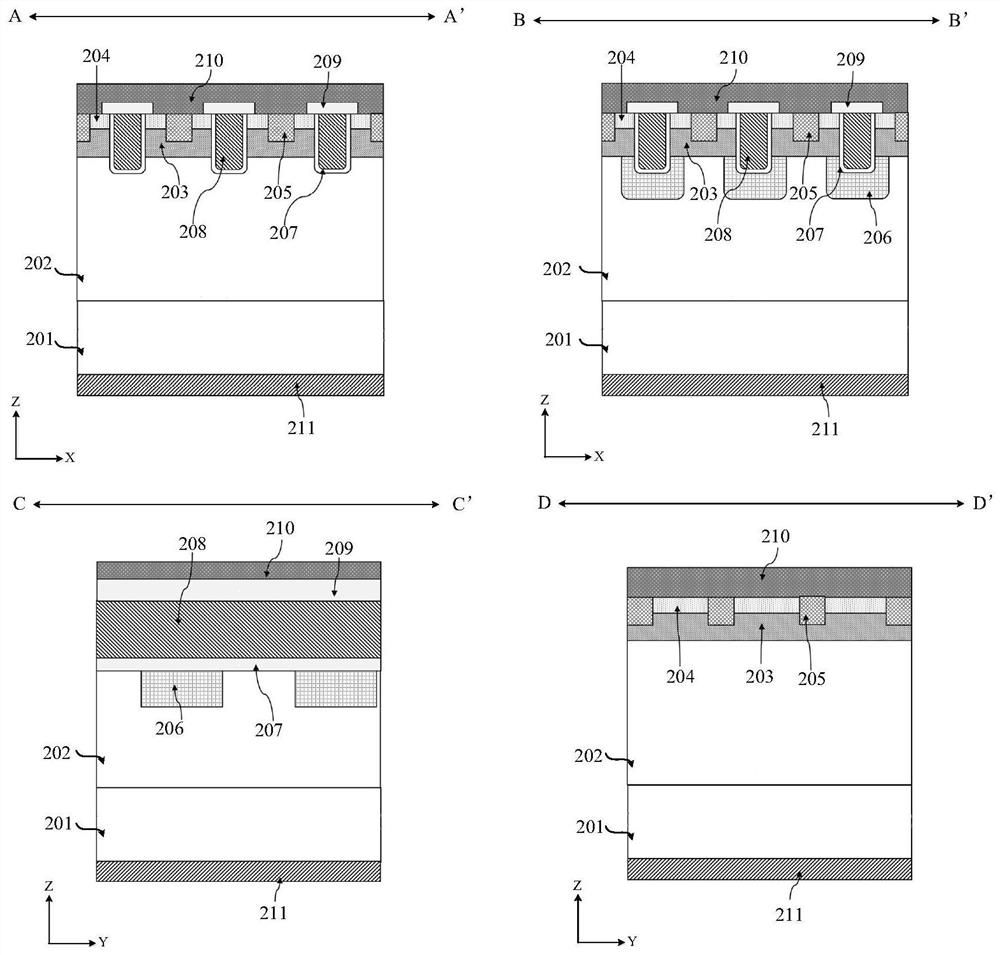

[0083] Such as figure 2 and image 3 As shown, the embodiment of the present disclosure provides a cell structure 200 of a silicon carbide device, including a substrate 201, a drift layer 202, a well region 203, a source region (not marked in the figure), a shield region 206, and a gate trench ( Not marked in the figure), gate dielectric layer 207 , gate 208 , interlayer dielectric layer 209 , source metal layer 210 and drain metal layer 211 .

[0084] It should be noted that, in this embodiment, the following "horizontal" refers to "X direction", "longitudinal" refers to "Y direction", "width" refers to "width in X direction", and depth refers to "Z direction". depth".

[0085] It should be noted that, in order to figure 2 The shapes and positions of the source region (not marked in the figure), the shielding region 206, the gate trench (not marked in the figure), the gate dielectric layer 207 and the gate 208 are clearly shown in the figure, so figure 2 The substrate ...

Embodiment 2

[0108] Such as Figure 4 and Figure 5 As shown, the embodiment of the present disclosure provides a cell structure 300 of a silicon carbide device, including a substrate 301, a drift layer 302, a well region 303, a source region (not marked in the figure), a shielding region 306, and a gate trench ( Not marked in the figure), gate dielectric layer 307 , gate 308 , interlayer dielectric layer 309 , source metal layer 310 and drain metal layer 311 .

[0109] It should be noted that, in this embodiment, the following "horizontal" refers to "X direction", "longitudinal" refers to "Y direction", "width" refers to "width in X direction", and depth refers to "Z direction". depth".

[0110] It should be noted that, in order to Figure 4 The shapes and positions of the source region (not marked in the figure), the shielding region 306, the gate trench (not marked in the figure), the gate dielectric layer 307 and the gate 308 are clearly shown in the figure, so Figure 4 The substr...

Embodiment 3

[0134] Such as Figure 6 and Figure 7 As shown, the embodiment of the present disclosure provides a cell structure 400 of a silicon carbide device, including a substrate 401, a drift layer 402, a well region 403, a source region (not marked in the figure), a shield region 406, a storage region 412, a gate Trench (not marked in the figure), gate dielectric layer 407, gate 408, interlayer dielectric layer 409, source metal layer 410 and drain metal layer 411.

[0135] It should be noted that, in this embodiment, the following "horizontal" refers to "X direction", "longitudinal" refers to "Y direction", "width" refers to "width in X direction", and depth refers to "Z direction". depth".

[0136] It should be noted that, in order to Figure 6 The shapes and positions of the source region (not marked in the figure), the shielding region 406, the gate trench (not marked in the figure), the gate dielectric layer 407 and the gate 408 are clearly shown in the figure, so Figure 6 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More