Anti-EMI SGT device

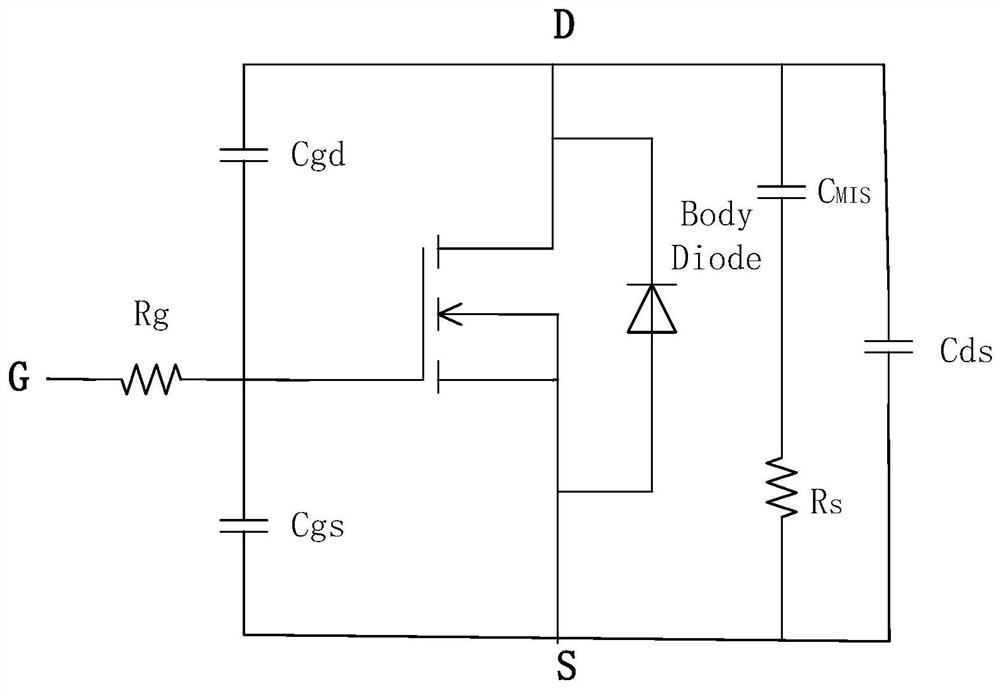

A device and conductive type technology, applied in the field of SGT devices, can solve the problems of increasing the possibility of voltage shock dv/dt failure of the device and EMI noise, electromagnetic pollution of components and equipment, parasitic triode turn-on, etc., to reduce Miller capacitance Cgd, reduce EMI electromagnetic radiation noise, reduce the effect of switching oscillation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

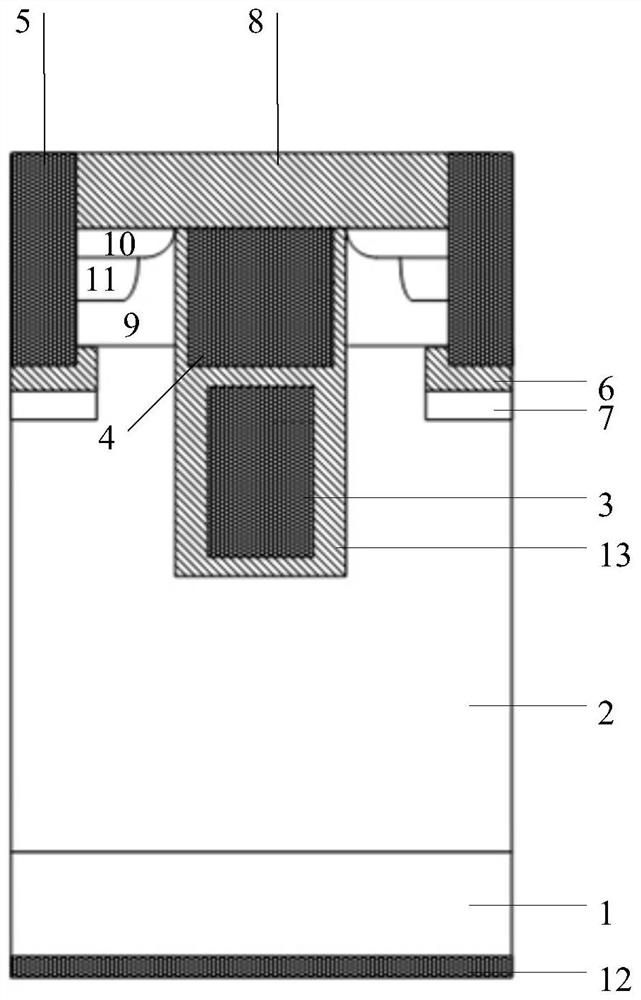

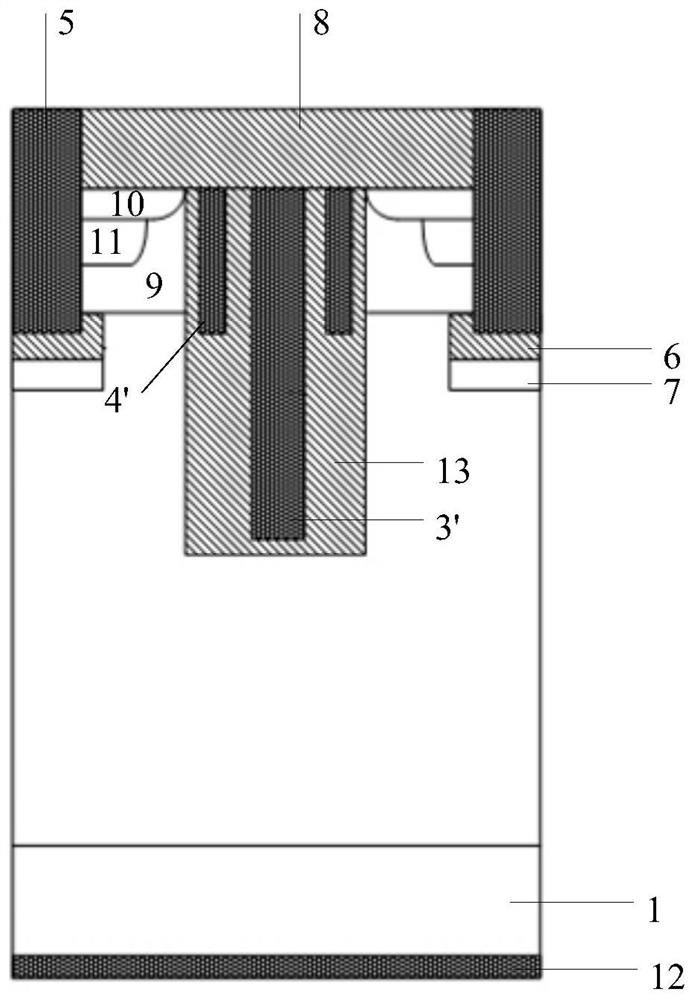

[0039] refer to Figures 1 to 3 As shown, the present invention provides an anti-EMI SGT device, comprising a substrate 1 of the first conductivity type; an epitaxial layer 2 of the first conductivity type, located on the upper surface of the substrate 1 of the first conductivity type; a trench gate structure , located in the epitaxial layer 2 of the first conductivity type, and extending along the thickness direction of the epitaxial layer 2 of the first conductivity type; the trench gate structure includes a gate trench, and a shield gate located in the gate trench 3 / 3' and polysilicon gate 4 / 4'; the trench source structure is located above the side surface of the epitaxial layer 2 of the first conductivity type and extends along the thickness direction of the epitaxial layer 2 of the first conductivity type; the trench source The structur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More