Semiconductor device and preparation method thereof, and semiconductor packaging structure

A packaging structure and semiconductor technology, applied in the field of microelectronics, can solve problems affecting the performance and stability of semiconductor devices, and achieve the effects of improving packaging flexibility, improving performance and stability, and reducing parasitic inductance and parasitic resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] For purposes of the present invention, technical solutions and advantages clearer, the following examples in conjunction with the accompanying drawings embodiments of the present invention, by way of specific embodiments, fully describe the present invention. Obviously, the described embodiments are part of the embodiments of the present invention, but not all embodiments of the present invention based on the embodiments, those of ordinary skill in all other embodiments obtained in Example without creative work, fall within the scope of the present invention.

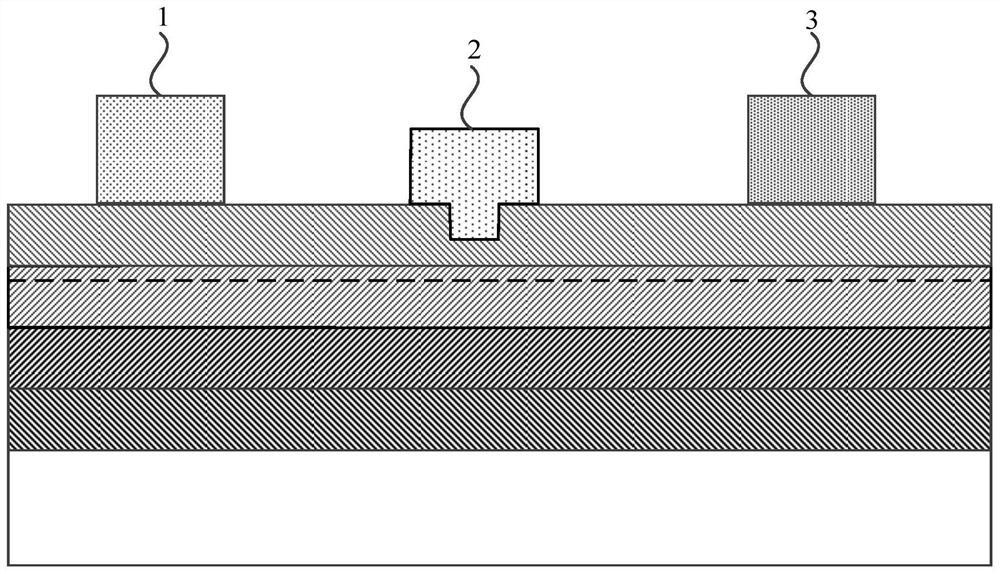

[0052] figure 1 It is a schematic cross-sectional structure of a semiconductor device of the prior art, such as figure 1 As shown in the prior art, a source electrode, gate electrode 2 and the drain 3 on the same surface of the semiconductor device, the semiconductor device 1 of the source, from the same surface of the gate electrode 3 and the drain 2 load signal, leading to the interconnection leads more, because the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More