Manufacturing method for SiC MOSFET device and SiC MOSFET device

A manufacturing method and device technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of strict polysilicon oxidation process requirements, difficulty in accurately controlling the channel size, and high process difficulty, and achieve a large improvement. The effect of current density output capability, increasing current lateral output path, simple and stable process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

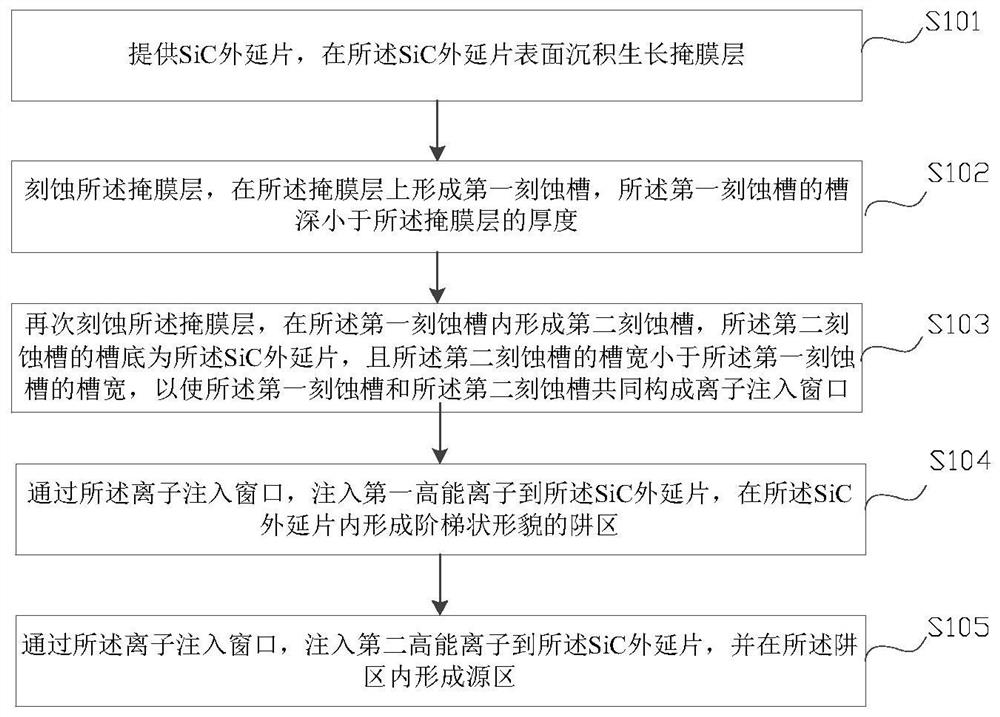

[0050] figure 1 It is a schematic flowchart of a manufacturing method of a SiC MOSFET device shown in an embodiment of the present disclosure. Figure 2-Figure 8 It is a schematic cross-sectional structure formed by related steps of a manufacturing method of a SiC MOSFET device shown in an embodiment of the present disclosure. Below, refer to figure 1 with Figure 2-Figure 8 The detailed steps of an exemplary method of the method for manufacturing a SiC MOSFET device proposed by the embodiments of the present disclosure will be described.

[0051] Such as figure 1 As shown, the SiC MOSFET manufacturing method of this embodiment includes the following steps:

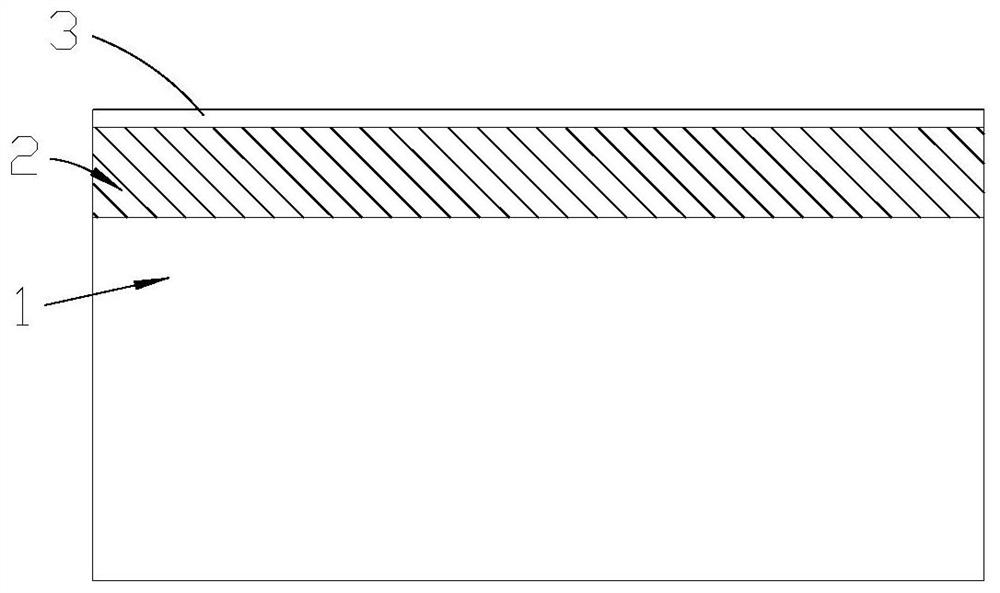

[0052] Step S101 : providing a SiC epitaxial wafer 1 , and depositing a growth mask layer 2 on the surface of the SiC epitaxial wafer 1 .

[0053] In specific implementation, the material for forming the mask layer in the above steps is SiO 2 , SiN, AlN, polysilicon and amorphous silicon.

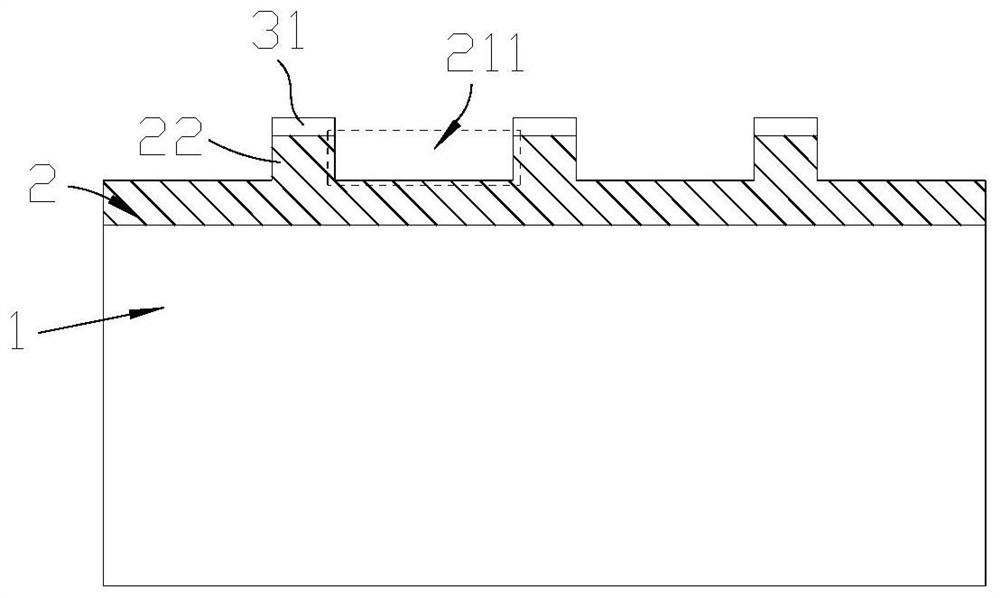

[0054] Step S102 : etchi...

Embodiment 2

[0082] On the basis of Embodiment 1, this embodiment provides a method using SiO 2 The manufacturing method of N-type SiCMOSFET device as mask layer material, such as figure 1 shown, including the following steps:

[0083] Step S101 : providing an N-type SiC epitaxial wafer 1 , and depositing a growth mask layer 2 on the surface of the N-type SiC epitaxial wafer 1 .

[0084] In specific implementation, the material for forming the mask layer in the above steps is SiO 2 , the thickness of the mask layer is 2um.

[0085] Step S102 : Etching the mask layer 2 to form a first etching groove 211 on the mask layer. The depth of the first etching groove 211 is smaller than the thickness of the mask layer 2 .

[0086] Specifically, the etching slope angle of the first etching groove 211 in the above step S102 is 90 degrees, and the groove depth is 1.0 um to 1.2 um.

[0087] In the embodiment of the present disclosure, specifically, as figure 2 with image 3 As shown, the above s...

Embodiment 3

[0110] Figure 9 It is a schematic cross-sectional structure diagram of a SiC MOSFET device shown in an embodiment of the present disclosure. Such as Figure 9 As shown, a SiC MOSFET device includes: a SiC epitaxial wafer 1 , a well region 4 with a stepped shape in the SiC epitaxial wafer 1 , and a source region 5 located in the well region 4 .

[0111] It also includes a gate insulating layer 6 located above the SiC epitaxial wafer 1 and between two adjacent source regions 5 , and a polysilicon gate 7 located on the gate insulating layer 6 .

[0112] It also includes an interlayer dielectric layer 8 covering the polysilicon gate, a front metal layer 9 covering the SiC epitaxial wafer 1 and the interlayer dielectric layer 8 , and a back metal layer 10 covering the back of the SiC epitaxial wafer 1 .

[0113] Specifically, the step-shaped well region 4 includes a first well region 41 flush with the surface of the SiC epitaxial wafer 1 and a second well region 42 located below...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More