Silicon carbide UMOSFET device integrated with SBD, and preparation method thereof

A silicon carbide and device technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as affecting device reliability, increasing system area, and large forbidden band width.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

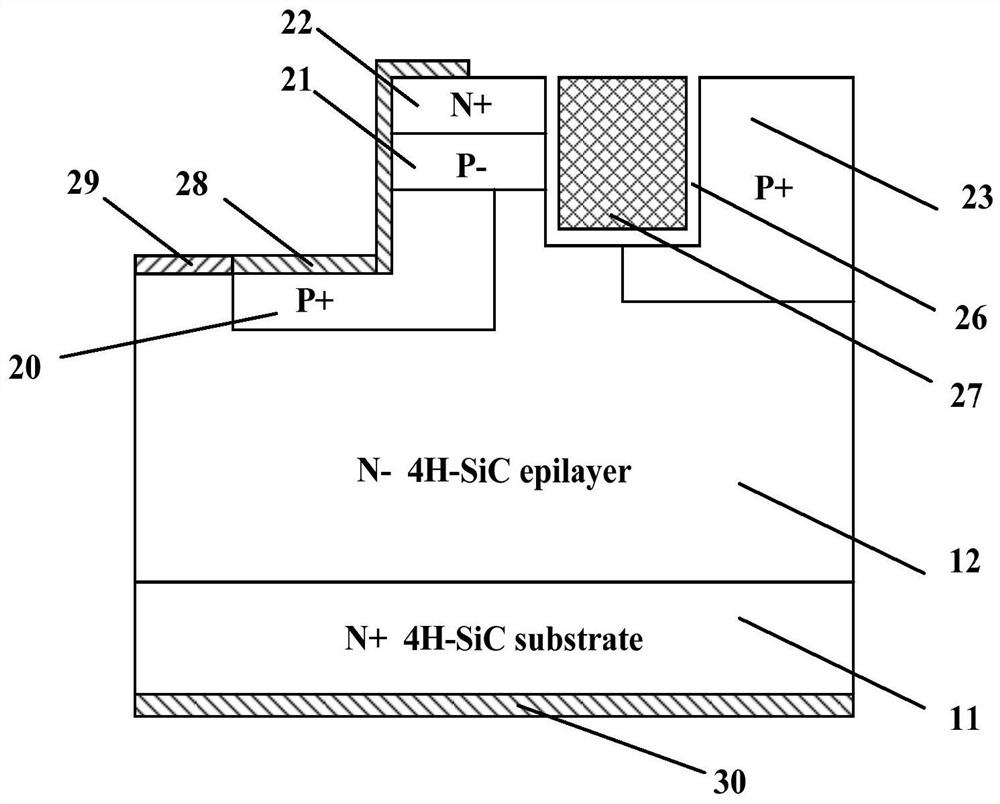

[0057] like figure 1 The illustrated embodiment provides an SBD-integrated silicon carbide UMOSFET device, which includes: a bottom-up third metal 30 , an N+ substrate 11 and an N- epitaxial layer 12 .

[0058] The N- epitaxial layer 12 has a first P+ implantation region 23 , a second P+ implantation region 20 , a first spacer (not shown) and a first P-well region 21 . The first P-well region 21 has a first N+ implantation region 22 (the depth of the first P-well region 21 is greater than the depth of the first N+ implantation region 22 ).

[0059] The device also includes: a gate dielectric layer 26 covering the bottom and sidewalls of the first trench 24; a gate 27 located on the gate dielectric layer 26 and filling the first trench 24; a first metal 28, the first metal 28 A first ohmic contact is formed on the upper surface of part of the first N+ implantation region 22, the side surface of the first P- well region 21, and the upper surface of the second P+ implantation re...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More