Manufacturing method of semiconductor structure and semiconductor structure

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as short circuit of upper and lower electrodes of capacitors, affecting the electrical performance of semiconductor structures, and difficulty in controlling the dimensional accuracy of capacitor holes.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] It can be seen from the background art that the yield rate and electrical performance of the semiconductor structure in the prior art need to be improved.

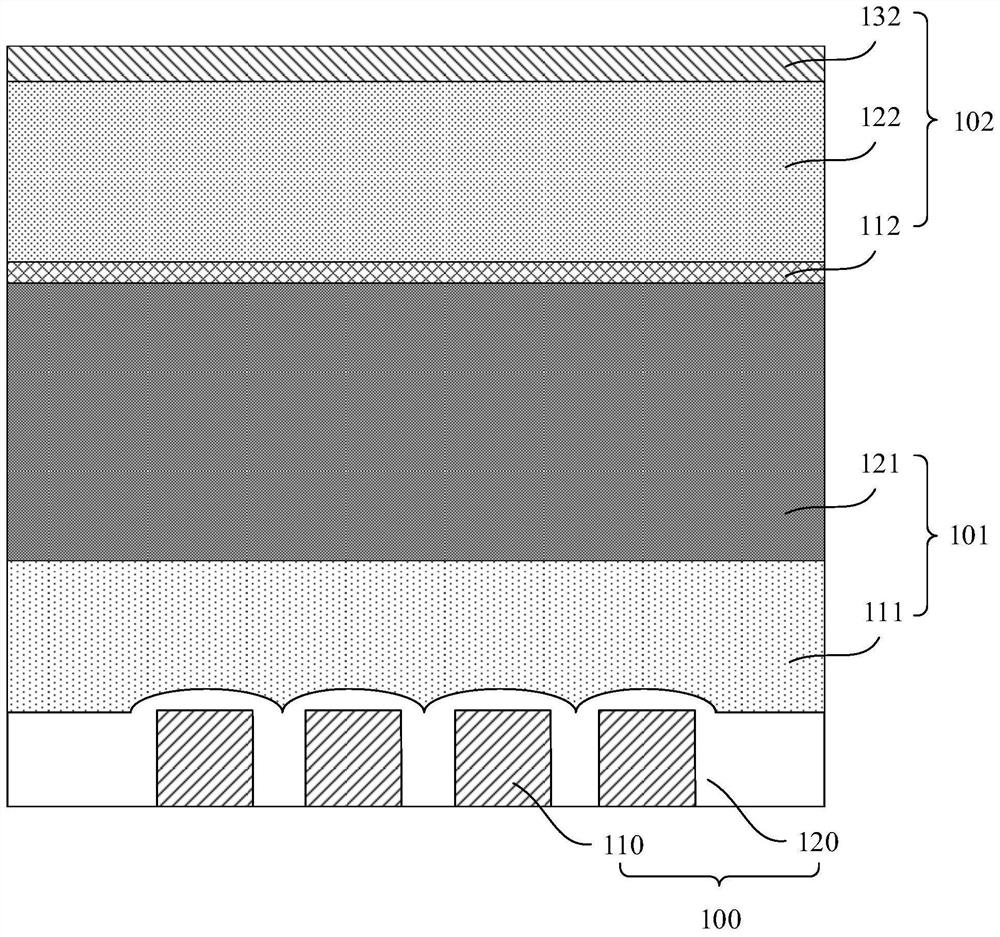

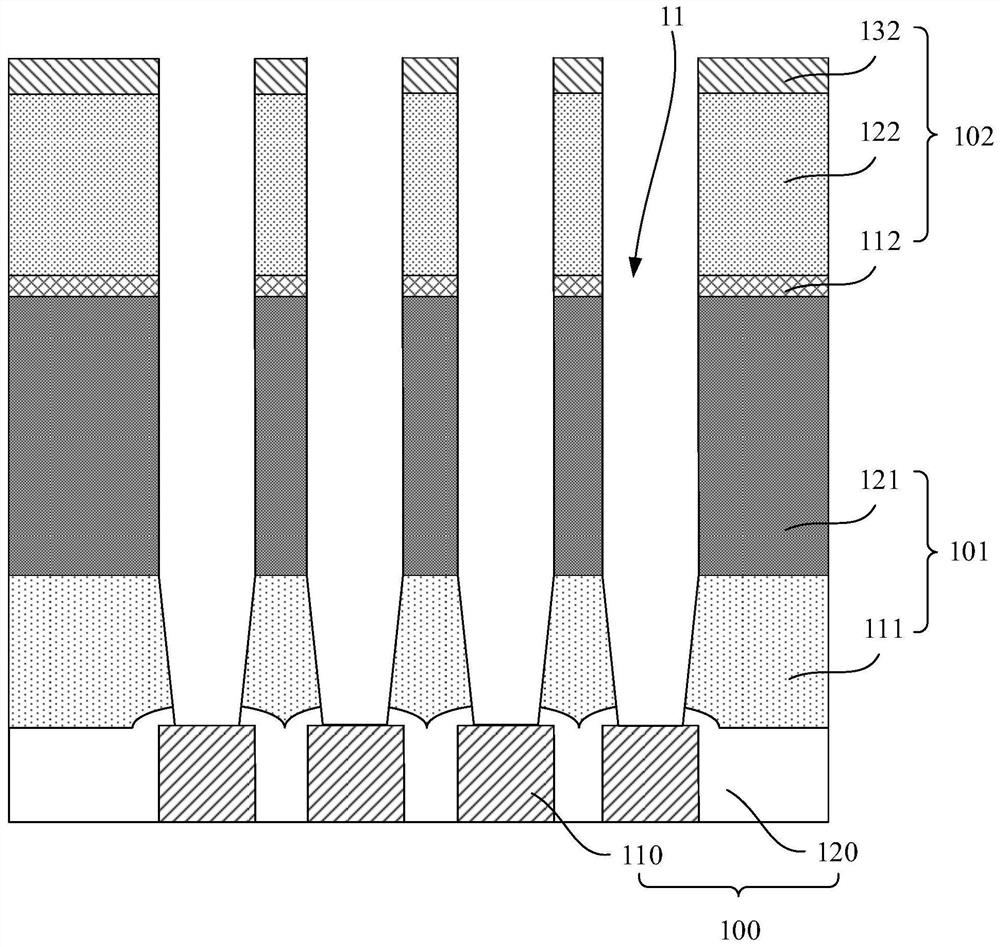

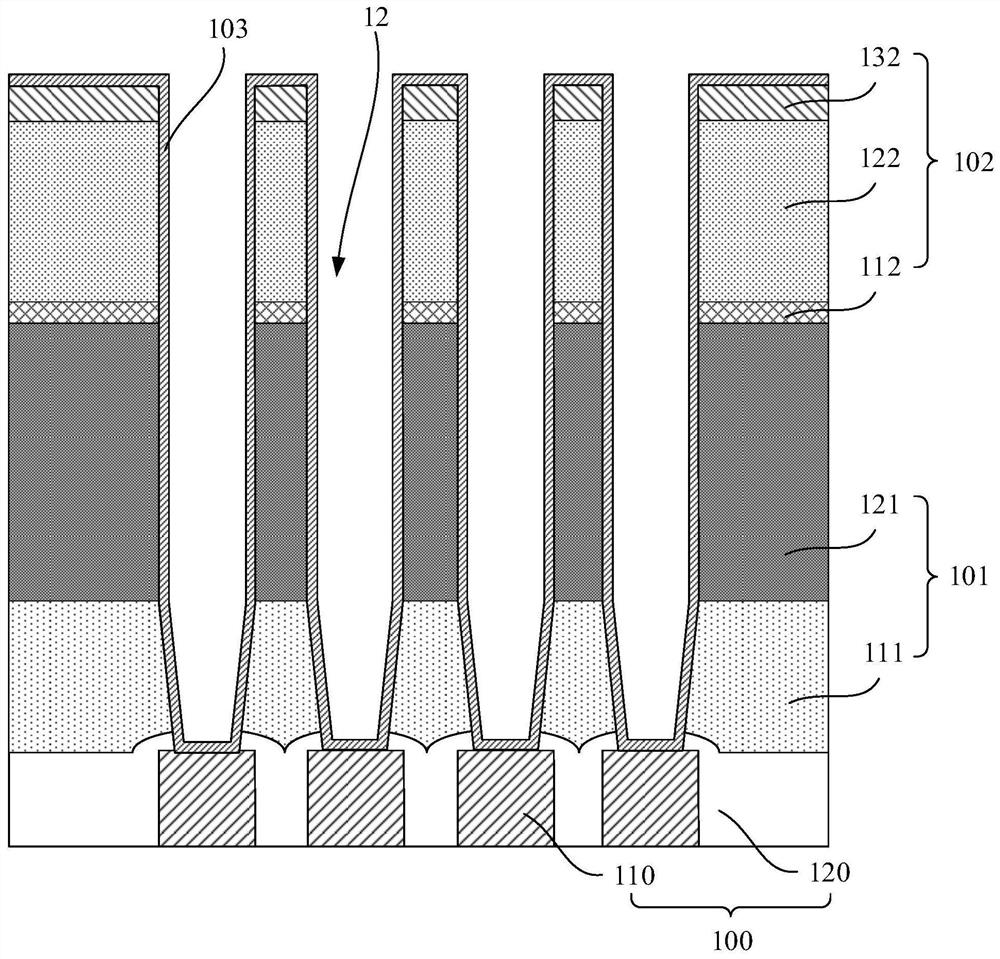

[0027] It is found through analysis that in order to form capacitor holes with a large aspect ratio, a first mask layer and a second mask layer are usually sequentially formed on the first support layer, and the first mask layer is generally a single-layer structure. Etching part of the second mask layer, part of the first mask layer and part of the first support layer until the capacitive contact structure is exposed to form the capacitive hole, due to the gap between the mask plate used to form the capacitive hole and the capacitive contact structure The alignment error and the over-etching of the first supporting layer by the etching process easily make the opening size of the bottom of the capacitor hole larger than the opening size of the top of the capacitor hole. Specifically, the intersection of the side wal...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com