Semiconductor structure and forming method thereof

A semiconductor and storage area technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as waste, reduced wafer pass rate, overlay error, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

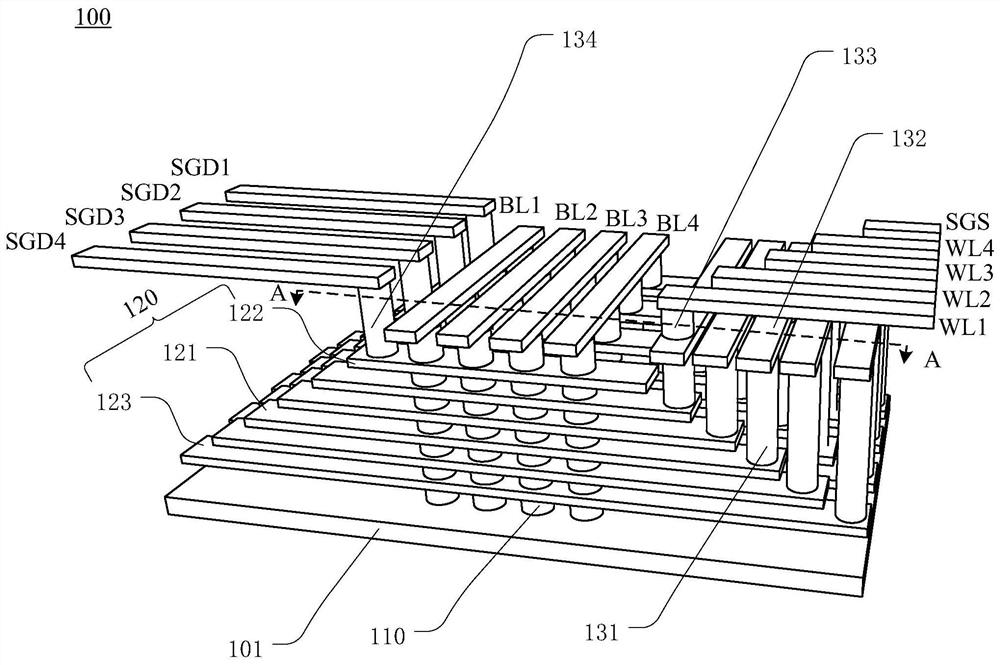

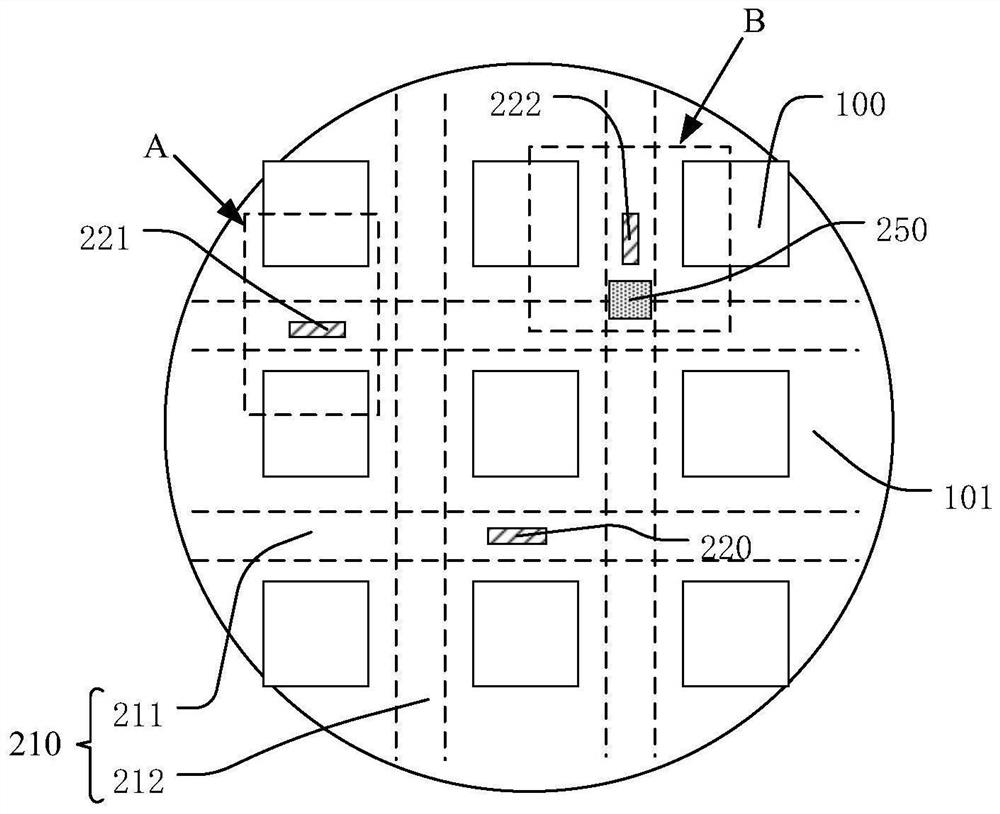

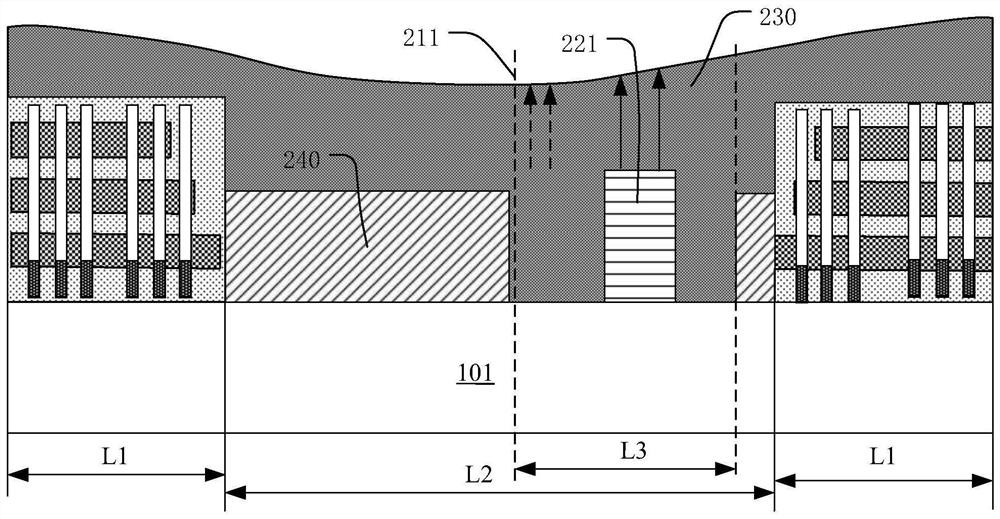

[0046] Hereinafter, the present invention will be described in more detail with reference to the accompanying drawings. In the various figures, identical elements are indicated with similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale. Also, some well-known parts may not be shown. For simplicity, the semiconductor structure obtained after several steps, including all layers or regions that have been formed, may be depicted in one figure.

[0047] It should be understood that when describing the structure of a device, when a layer or a region is referred to as being "on" or "over" another layer or another region, it may mean being directly on another layer or another region, or Other layers or regions are also included between it and another layer or another region. And, if the device is turned over, the layer, one region, will be "below" or "beneath" the other layer, another region.

[0048] The invention can be em...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More