Chip packaging method, chip and electronic device

A packaging method and chip technology, applied in the direction of electric solid-state devices, electrical components, semiconductor devices, etc., can solve problems such as secondary pollution, pollutant splashing, and quality degradation of intelligent power modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

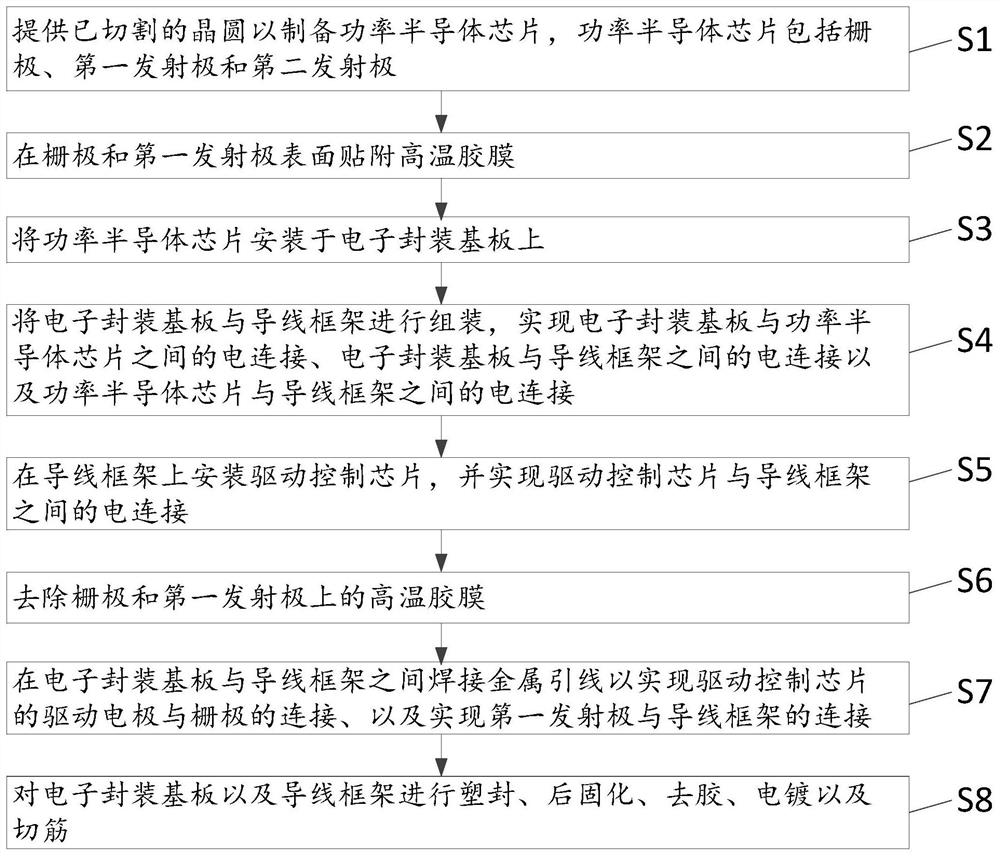

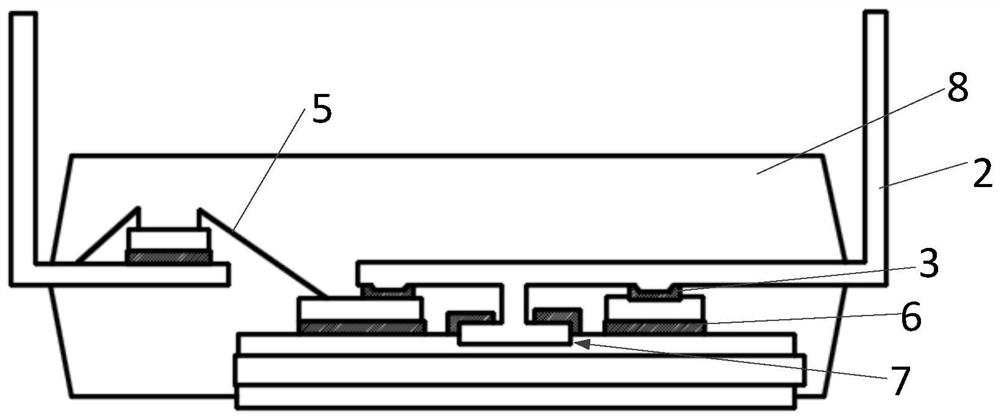

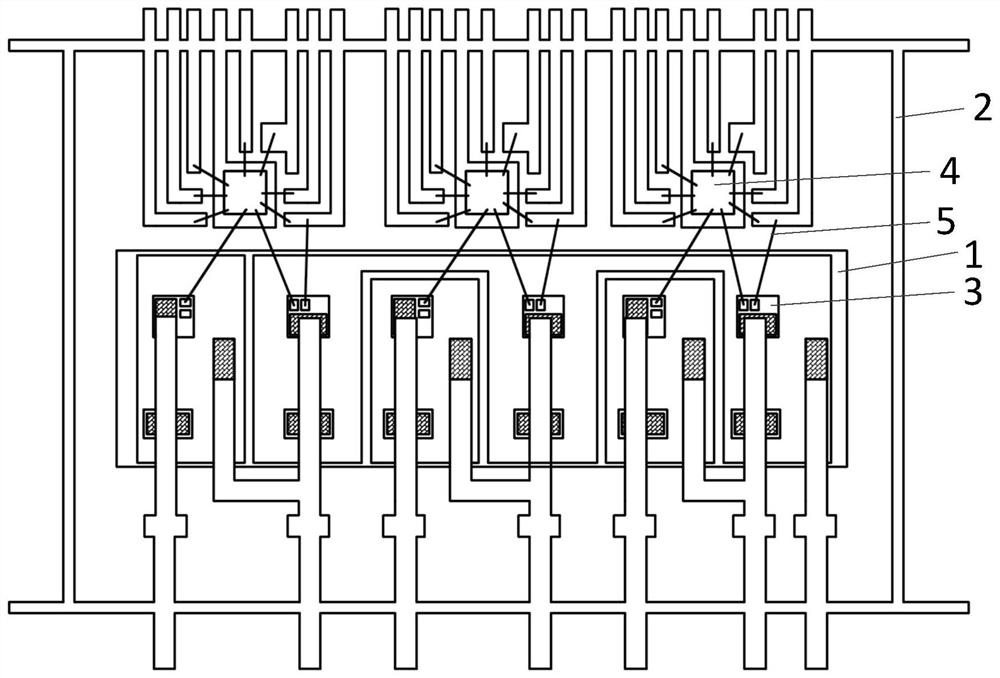

[0046] Such as figure 1 to combine image 3 and Figure 5-Figure 6 As shown, the present application provides a chip packaging method, which is used to solve the problem of polluting the grid 31 generated during the bonding process of the lead frame 2 and the chip. The specific steps are as follows:

[0047] S1: Provide a diced wafer to prepare a power semiconductor chip 3, the power semiconductor chip 3 includes a gate 31, a first emitter 32 and a second em...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More