Preparation method of compound semiconductor device and compound semiconductor device

A semiconductor and compound technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of quantum well layer source region defects, performance damage, photoelectric and signal crosstalk, etc., to avoid Signal crosstalk, the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

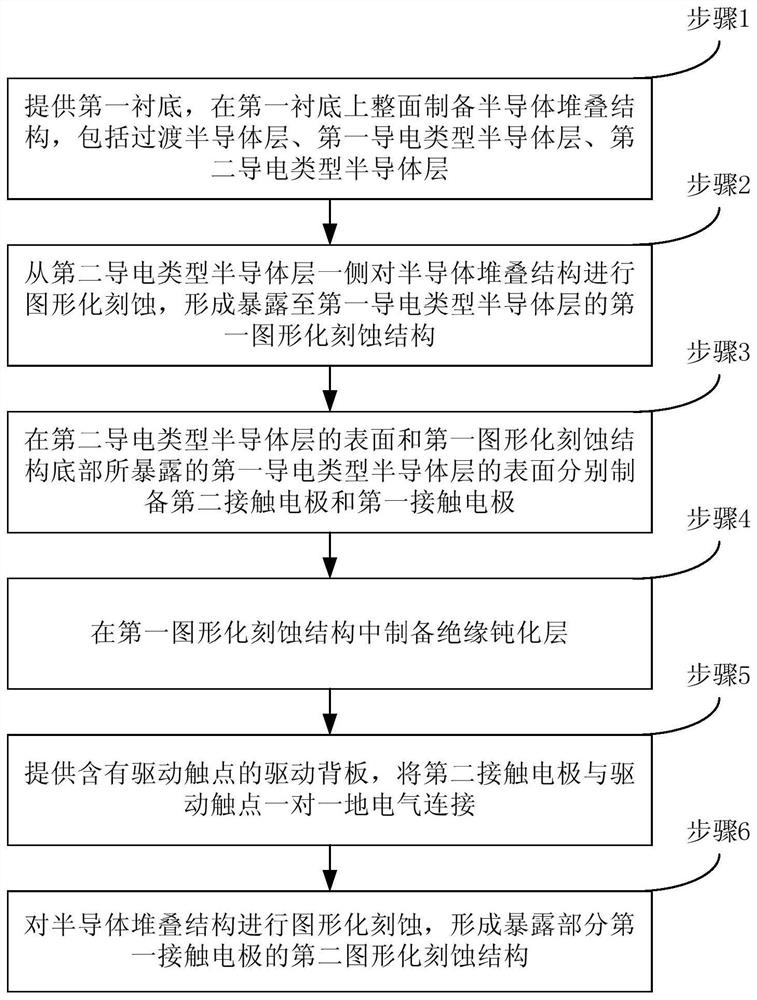

[0091] like figure 2 As shown, the method for preparing a compound semiconductor device provided by the embodiment of the present invention mainly includes the following steps:

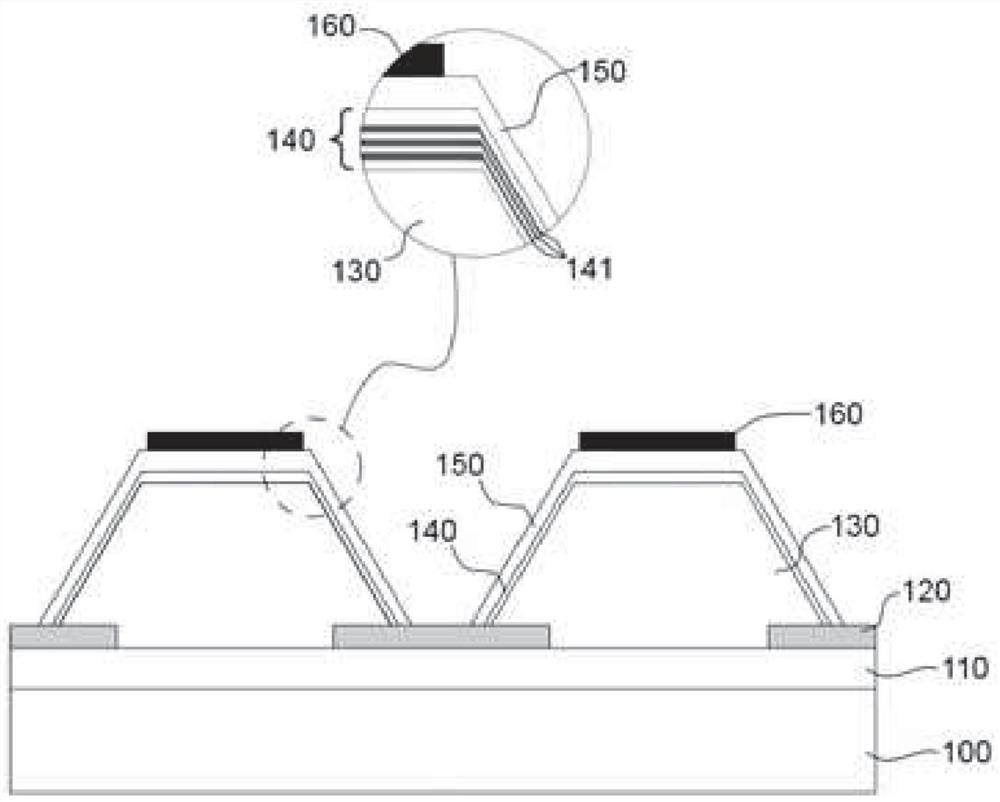

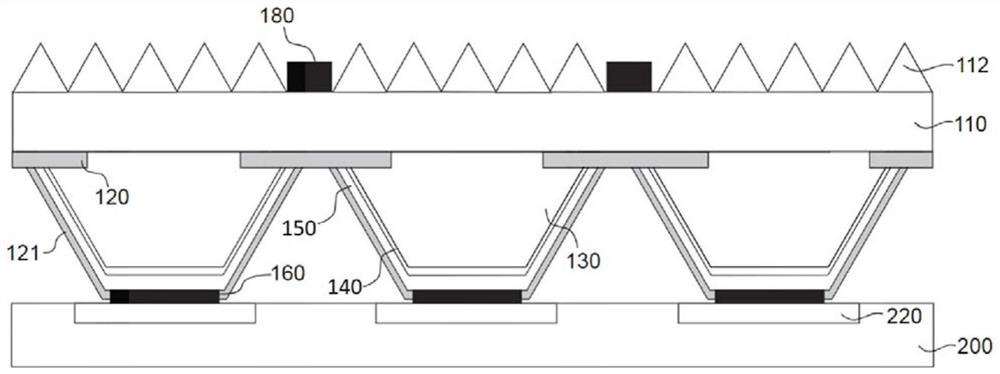

[0092] Step 1. Provide a first substrate, and prepare a semiconductor stack structure on the entire surface of the first substrate. The semiconductor stack structure includes a transition semiconductor layer stacked outward from the surface of the first substrate, a first conductivity type semiconductor layer, a second conductivity type type semiconductor layer;

[0093] Step 2: Perform patterned etching on the semiconductor stack structure from the side of the semiconductor layer of the second conductivity type to form a first patterned etched structure exposed to the semiconductor layer of the first conductivity type, wherein the first patterned etched structure penetrates The second conductivity type semiconductor layer does not penetrate through the first conductivity type semiconductor layer; ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More