Fully-depleted silicon-on-insulator substrate, transistor and preparation method and application thereof

A silicon-on-insulator and fully depleted technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as complex process flow of FinFET devices, difficult SOI substrate, and process cost reduction, and achieve the goal of suppressing substrate Bottom pulse current interference, reduced leakage, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

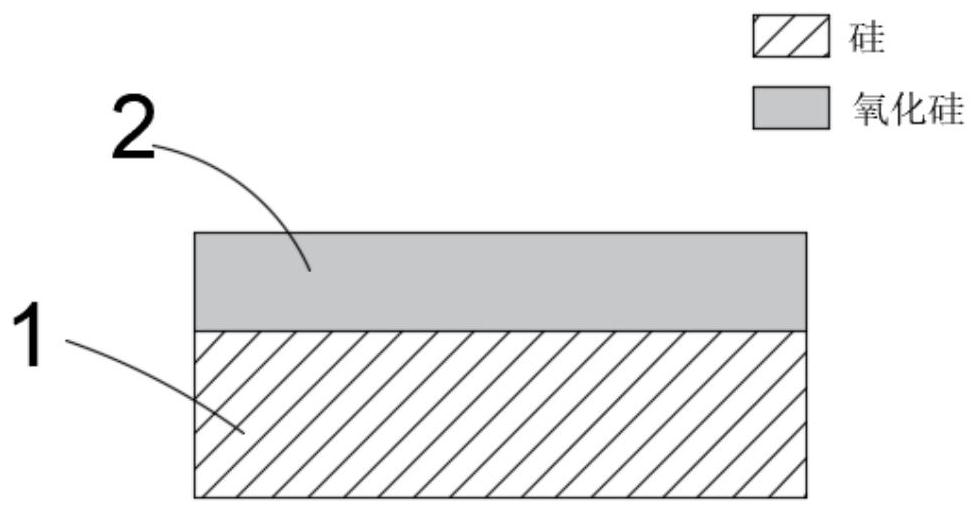

[0037] In the first step, a silicon oxide layer 2 is formed on the backing silicon layer 1 to obtain the following figure 1 The shape shown.

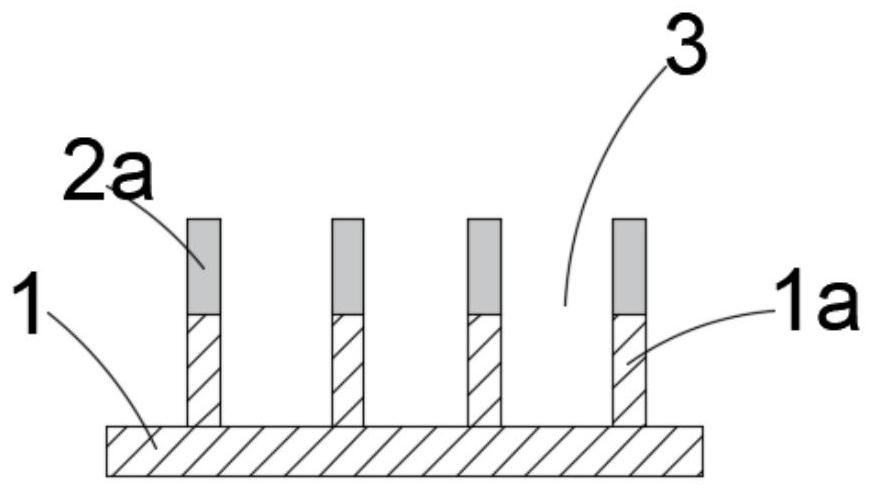

[0038] In the second step, photolithography and etching are carried out to form a plurality of grooves 3 in the silicon oxide layer 2, and obtain the following figure 2 The shape shown. Wherein, the trench 3 penetrates the silicon oxide layer 2 and goes deep into the backing silicon layer 1, so that the surface of the backing silicon layer 1 is divided into a plurality of silicon lines 1a, and the silicon oxide layer 2 is divided into a plurality of silicon oxide lines 2a. , the aspect ratio of the trench 3 is above 2:1, and the width of each of the silicon lines 1 a and the silicon oxide lines 2 a is 10 nm˜100 nm.

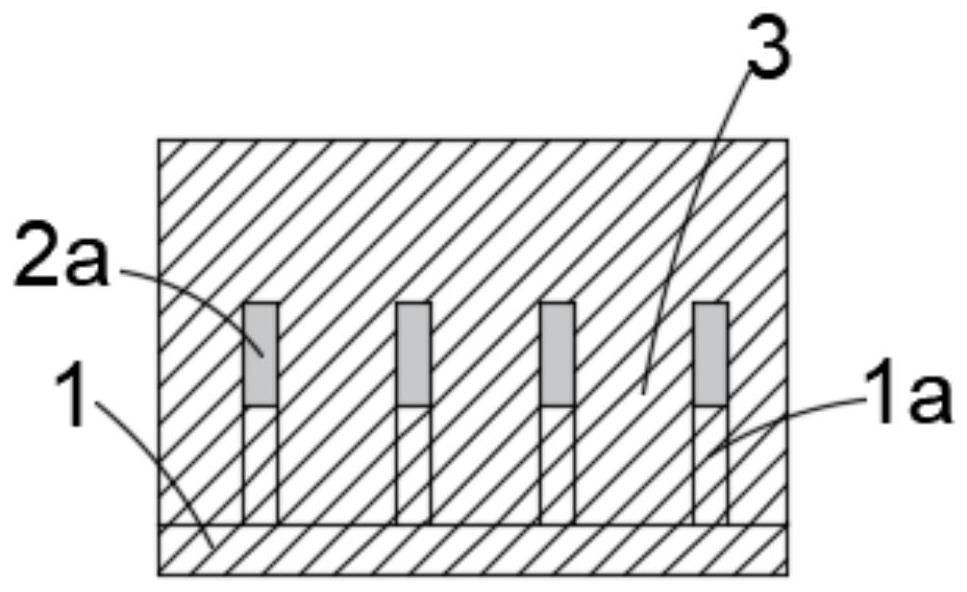

[0039] In the third step, the silicon top layer 3 is formed by selective epitaxial growth, and the following image 3 The shape shown.

[0040] The fourth step is to thin the silicon top layer 3 to obtain such as Fi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More