Forming method of semiconductor structure

A technology of semiconductor and dummy gate structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, and nanotechnology for information processing, etc. Effects of film etching, improvement of formation efficiency, and improvement of performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] As mentioned in the background art, the electrical performance of the GAA structure MOSFET in the prior art still needs to be improved. The following will describe in detail in conjunction with the accompanying drawings.

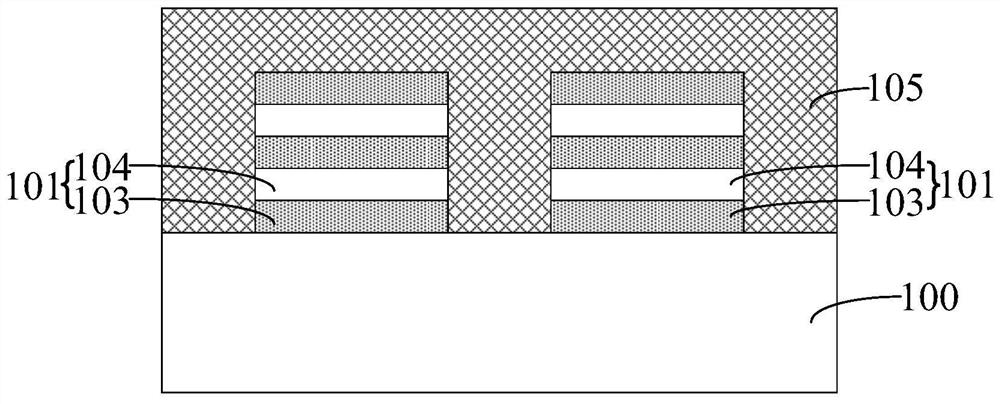

[0040] Please refer to figure 1 , providing a substrate 100; forming a plurality of fin structures 101 arranged in parallel along a first direction on the substrate 100, with isolation trenches (not marked) between adjacent fin structures 101, the The fin structure 101 includes several layers of sacrificial layers 103 overlapping along the normal direction of the surface of the substrate 100, and a channel layer 104 located between two adjacent layers of the sacrificial layers 103; formed on the substrate 100 Across the dummy gate structures 105 adjacent to the fin structures 101 , the dummy gate structures 105 extend along a second direction, and the first direction is perpendicular to the second direction.

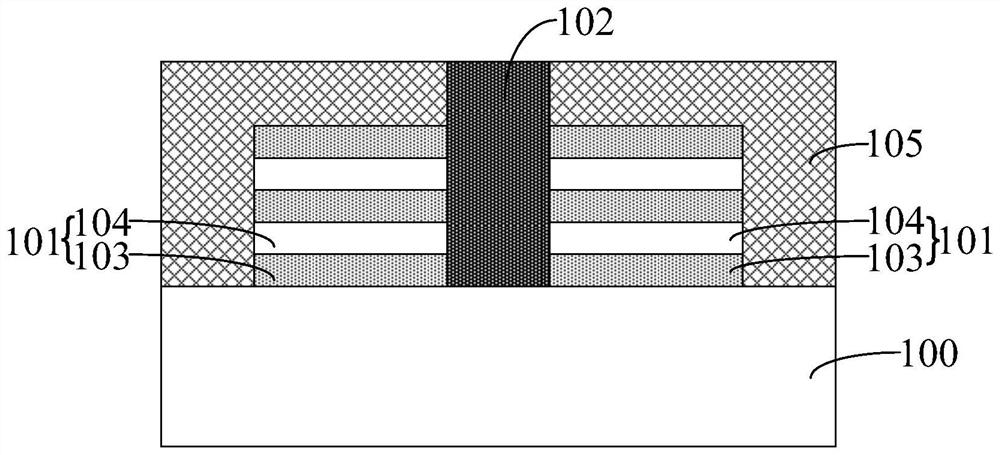

[0041] Please refer to figure 2 , rem...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More