A Parallel Accelerated Extraction Method of VLSI SPEF Parasitic Parameters

A large-scale integrated circuit and parasitic parameter technology, which is applied in the direction of electrical digital data processing, special data processing applications, multi-programming devices, etc., can solve the problems of technical stagnation, time-consuming, and low efficiency of static timing analysis of computing resources, etc. Achieve a good speed-up ratio and improve the response speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

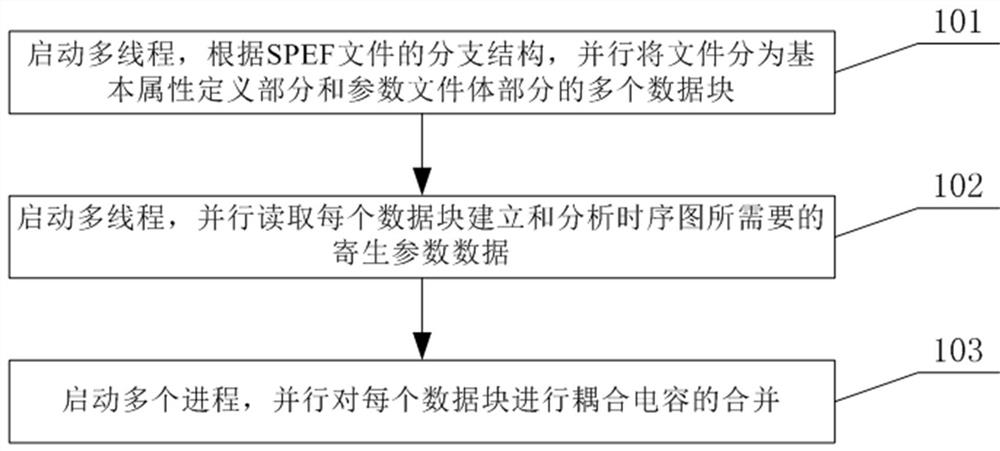

[0046] figure 1 For the parallel accelerated extraction method flow chart of VLSI SPEF parasitic parameters according to the present invention, reference will be made below figure 1 , to describe in detail the parallel accelerated extraction method of VLSI SPEF parasitic parameters of the present invention.

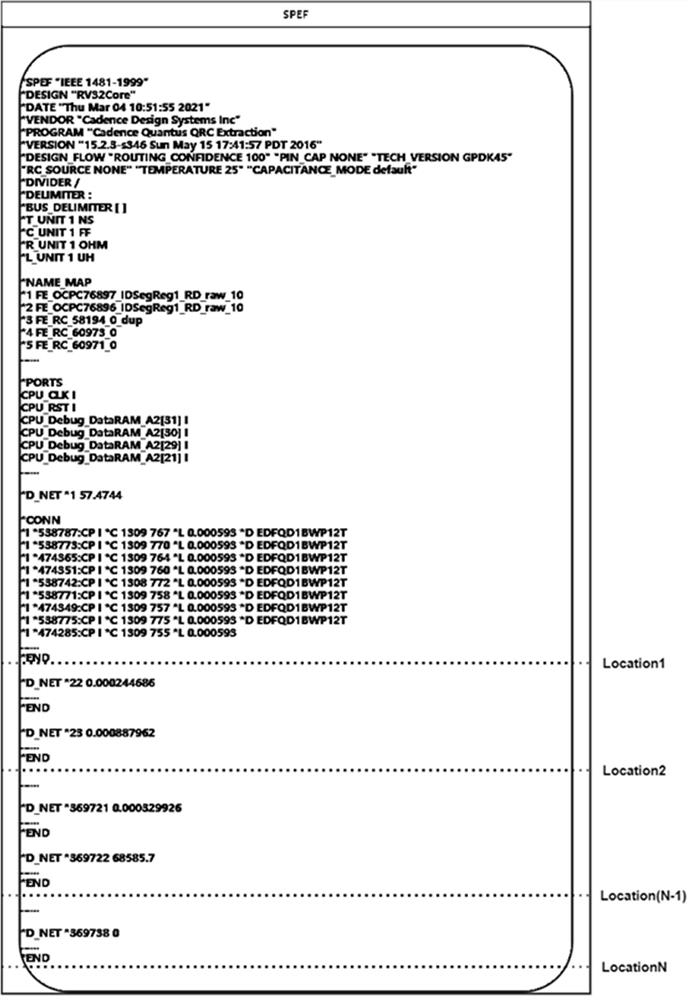

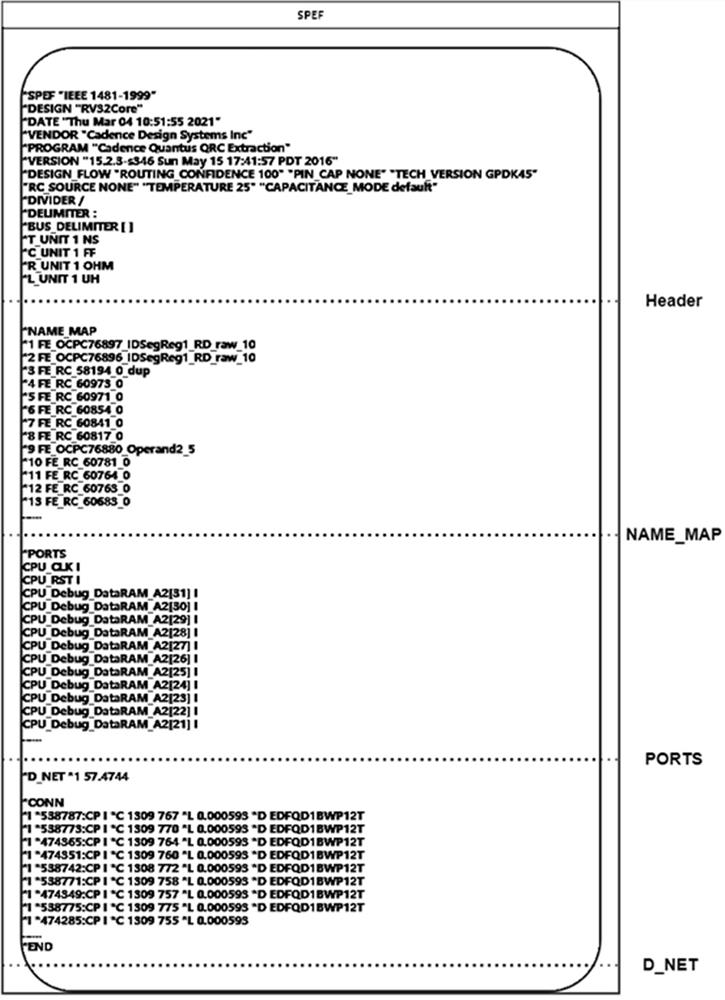

[0047] First, in step 101, read the SPEF file, start multithreading (process), and divide the file into a basic attribute definition part (Header) and a parameter file body including N data blocks (Partition) in parallel according to the branch structure of the SPEF file part.

[0048] It takes a long time to read the SPEF file using the normal single process (or thread) in the past, but many data blocks in it can be relatively independent after specific processing, and then can be graded and parallelized, and can obtain a considerable real-time operation speedup. Achieve computing load balancing.

[0049]In the embodiment of the present invention, in order to ensure t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More