Invisible semiconductor device and preparation method and application thereof

A semi-conductor and invisible technology, which is applied in the manufacture of semiconductor devices, electrical components, final products, etc., can solve the problems of damage to the uniformity of nano-column crystal quality, difficulty in guaranteeing the quality of epitaxial crystals, easy damage to graphene or nano-columns, etc., to achieve effective Facilitate reuse, controllable cost and long service life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

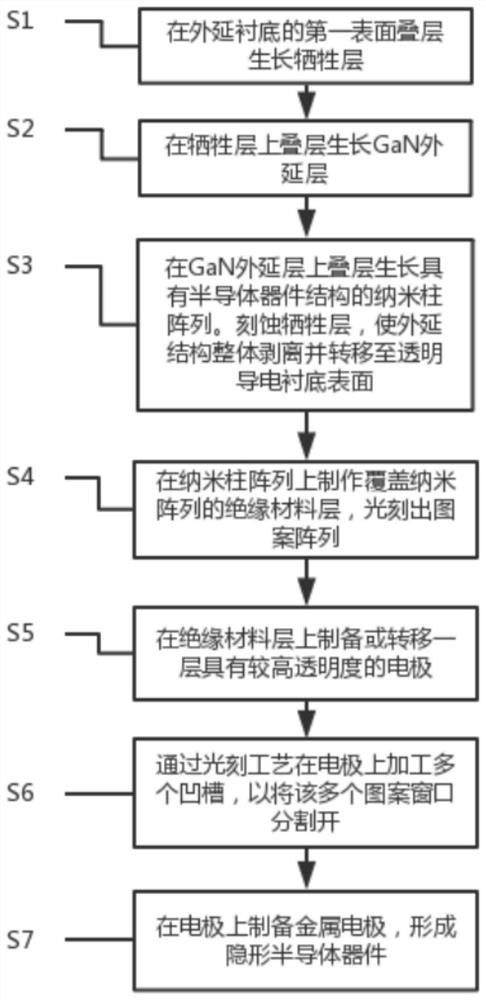

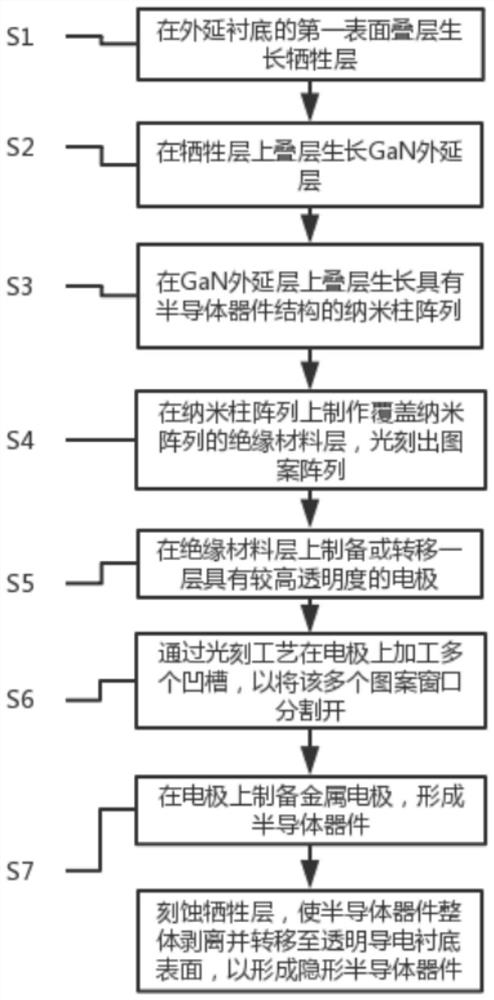

[0093] see figure 1 , an embodiment of the present invention provides a method for manufacturing a stealth semiconductor device, which includes:

[0094] S1. A sacrificial layer is stacked and grown on the first surface of the epitaxial substrate, and the total thickness of the sacrificial layer is H 0 , 1nm≤H 0 <100nm;

[0095] S2, stacking and growing a GaN epitaxial layer with pores or defects on the sacrificial layer, with a total thickness of H 1 , 1nm≤H 1 <600nm;

[0096] S3. On the GaN epitaxial layer, grow a nanocolumn array with a semiconductor device structure; prepare an etching electrode on the second surface of the epitaxial substrate opposite to the first surface, and make the etching electrode and the sacrificial electrode The layers are turned on, and then the sacrificial layer is removed by electrochemical etching, so as to peel off the epitaxial structure above the sacrificial layer as a whole, and transfer it to the surface of the transparent conductive...

Embodiment 1

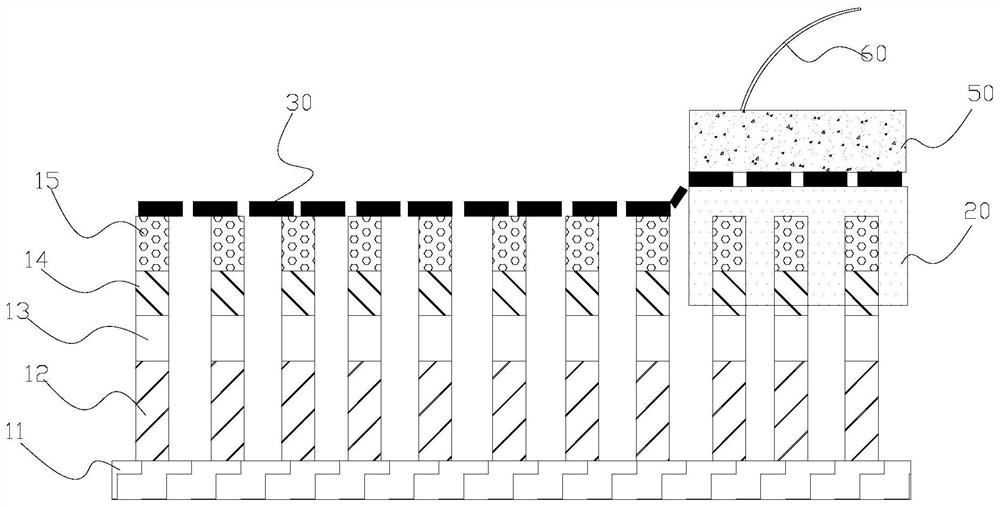

[0122] 1) First, place the silicon substrate in a molecular beam epitaxy (MBE) growth chamber for epitaxial growth, see Figure 4 , including the following steps:

[0123] In the first step, an AlN sacrificial layer 10 with a thickness of about 5 nm is grown on the front side of the n-type doped silicon (Si) substrate;

[0124] The second step is to grow a Si-doped GaN epitaxial layer 11 with a thickness of 20 nm and a thickness of 20 nm on the AlN sacrificial layer 10, and the doping concentration is 1×10 22 cm -3 ;

[0125] In the third step, a layer of Si-doped GaN nanocolumns 12 with a height of about 500 nm is grown on the GaN epitaxial layer 11, and the doping concentration is 1×10 22 cm -3 ;

[0126] The fourth step is to grow a layer of In with a thickness of 50nm on the GaN nanocolumn 12 0.3 Ga 0.7 N nanopillars13.

[0127] The fifth step, in the In 0.3 Ga 0.7 A layer of Al with a thickness of 10 nm is grown on the N nanopillar 13 0.2 Ga 0.8 N nanocolumns ...

Embodiment 2

[0137] This embodiment is basically the same as Embodiment 1, the difference is that In in this embodiment 1-n-x Al n Ga x There are 6 In in the N nanopillar 0.25 Ga 0.75 The superlattice-like structure of N(15nm) / GaN(5nm), that is, In 0.25 Ga 0.75 N (15nm) and GaN (5nm) are arranged alternately, with a total of 6 periods, in which the values of x in two adjacent layers are 0.75 and 1 respectively, and the values of n are both 0. In addition, there is a layer of hydrogel about 1 μm thick on the surface of the transferred transparent conductive substrate, which is used to fix the nanocolumns, and the device can be used as a light-emitting device.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Height | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More