Assembly line ADC background digital calibration method and device based on histogram statistics

A technique of histogram statistics and calibration method, applied in the direction of analog/digital conversion calibration/test, analog/digital conversion, electrical components, etc., can solve the problems that are not conducive to improving ADC signal-to-noise ratio and linearity, increasing system power consumption and algorithm Complexity, unable to guarantee calibration performance and other issues, to achieve the effect of improving signal-to-noise ratio and linearity, easy implementation, and high calibration accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

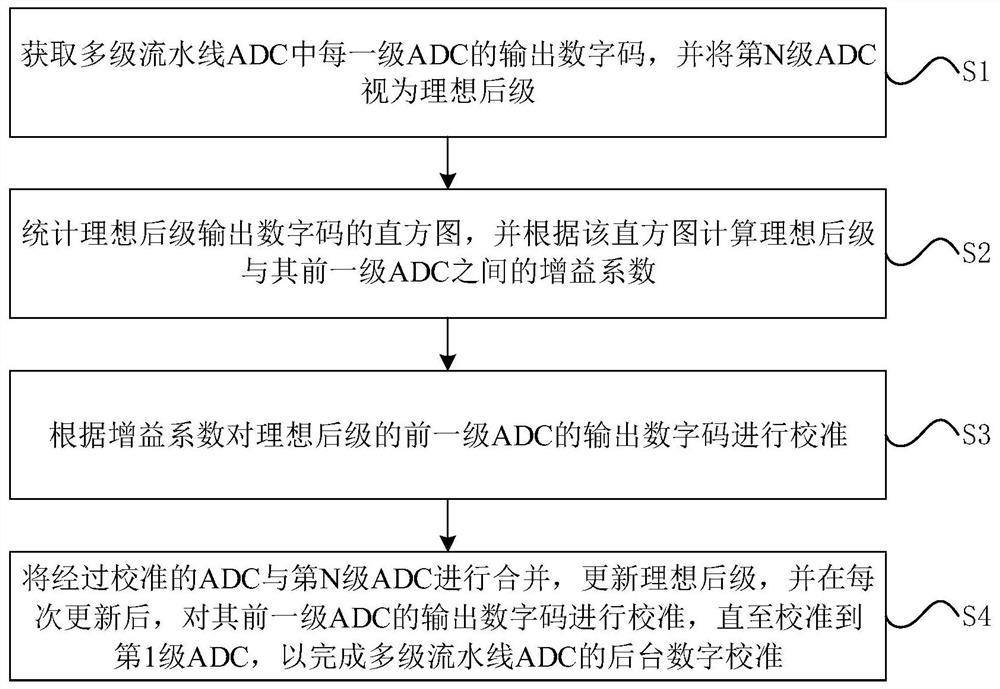

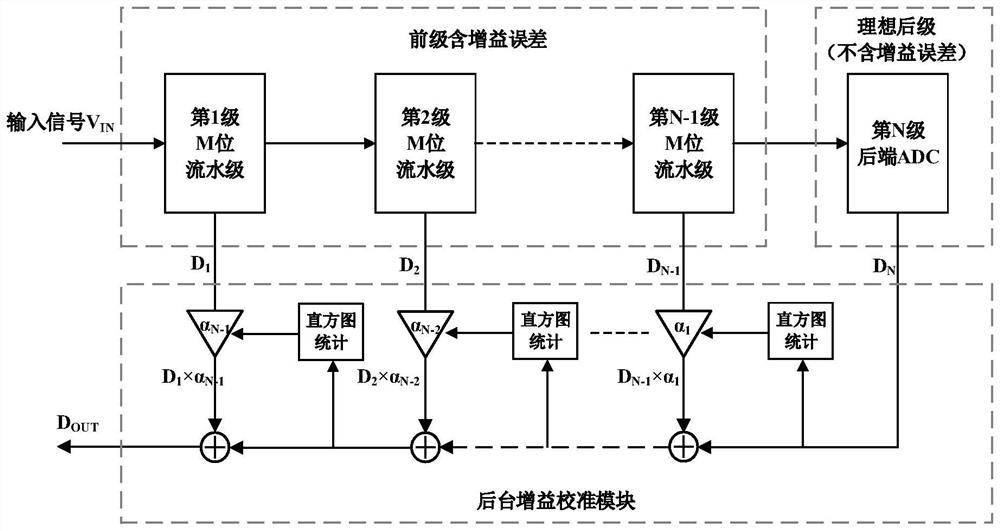

[0061] See Figure 1-2 , figure 1 It is a schematic diagram of a pipeline ADC background digital calibration method based on histogram statistics provided by an embodiment of the present invention, figure 2 It is a schematic diagram of the implementation process of a pipelined ADC background digital calibration method based on histogram statistics provided by the embodiment of the present invention; the method specifically includes the following steps:

[0062] S1: Obtain the output digital code of each stage of ADC in the multi-stage pipeline ADC, and regard the Nth stage of ADC as an ideal subsequent stage.

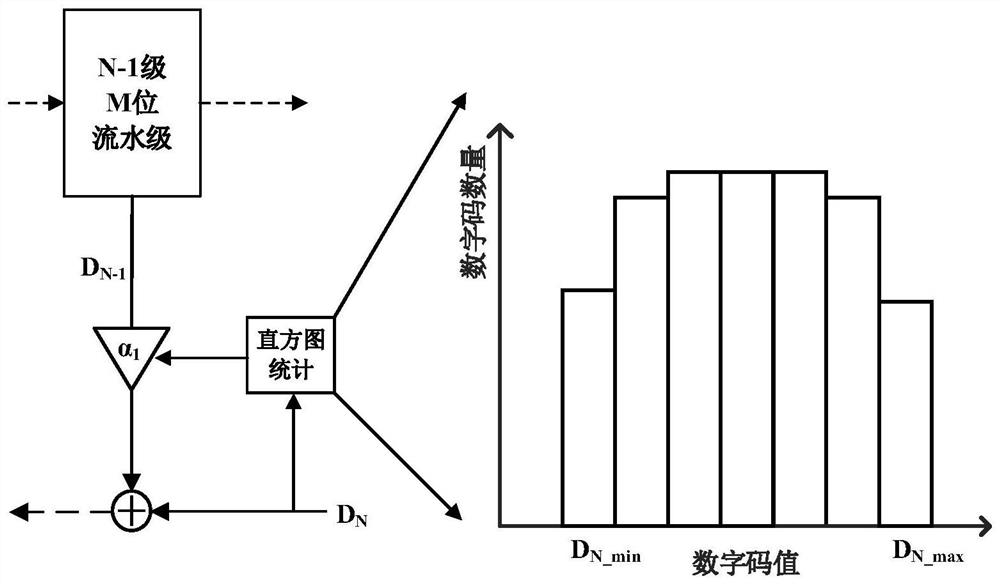

[0063] Specifically, in this embodiment, the N-stage pipeline ADC input signal V IN , After the pipeline ADC has been converted for a period of time, the background calibration is started. At this point, the output digital codes of the ADCs at all levels are obtained, denoted as D 1 、D 2 ...D N-1 、D N , and the default digital code D of the last stage of the pip...

Embodiment 2

[0098] As an optional embodiment of the present invention, after step S21 and before step S22 in the first embodiment, further includes: performing threshold screening on the histogram to remove digital codes caused by noise.

[0099] See Figure 5 , Figure 5 It is an example diagram of statistical results of histograms containing noise provided by the embodiment of the present invention. Since the actual pipeline ADC does not work ideally, considering that the kickback noise and thermal noise in the ADC will cause the change of the digital code, and the frequency of the change of the digital code caused by the noise is much smaller than the change of the input signal, so the threshold value is set up. filter.

[0100] The threshold screening method for statistical results can remove the influence of the expansion of the digital code range caused by noise, and ensure that the actual gain value is obtained.

[0101] After the digital code generated by the noise is removed, ...

Embodiment 3

[0104] The comparator voltage offset due to transistor mismatch and process production error will generate an offset voltage at the input terminal of the comparator, making the comparator judge wrongly. In order to reduce this effect, the pipeline ADC generally adds redundant bits so that the comparator can still work normally when the judgment is wrong, but this will affect the general calibration method. In order to eliminate this effect, this embodiment provides a calculation method for calculating the average gain.

[0105] As an optional embodiment of the present invention, when the present invention performs statistics on the histogram of the output digital code of the ideal rear stage, and calculates the gain coefficient between the ideal rear stage and its previous stage ADC according to the histogram, You can follow the steps below:

[0106] Segment the output digital code of the current ideal subsequent stage according to the output digital code of the previous stag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More