Surface planarization method of semiconductor device

A surface planarization and semiconductor technology, applied in the field of surface planarization of semiconductor devices, can solve the problems of unsolved terminal area planarization, polysilicon residue treatment without terminal area, etc. Achieve precise control of the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0039] A method for planarizing a surface of a semiconductor device, comprising the steps of,

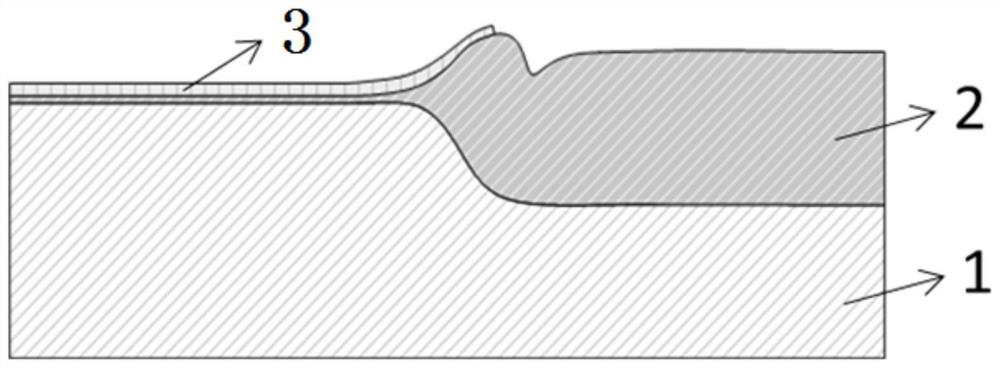

[0040] Step 1: If Figure 4 As shown, a cell region oxide layer 2 and silicon nitride 3 are deposited on a silicon substrate 1;

[0041] Step 2: If Figure 5 As shown, the open area formed by etching is oxidized to form an oxide layer 4 in the terminal area;

[0042] Step 3: If Figure 6 As shown, a hard mask layer 5 is deposited;

[0043] Step 4: If Figure 7 As shown, photolithography is performed first, and then the hard mask layer 5, the silicon nitride 3 and the oxide layer 2 of the cell region are etched;

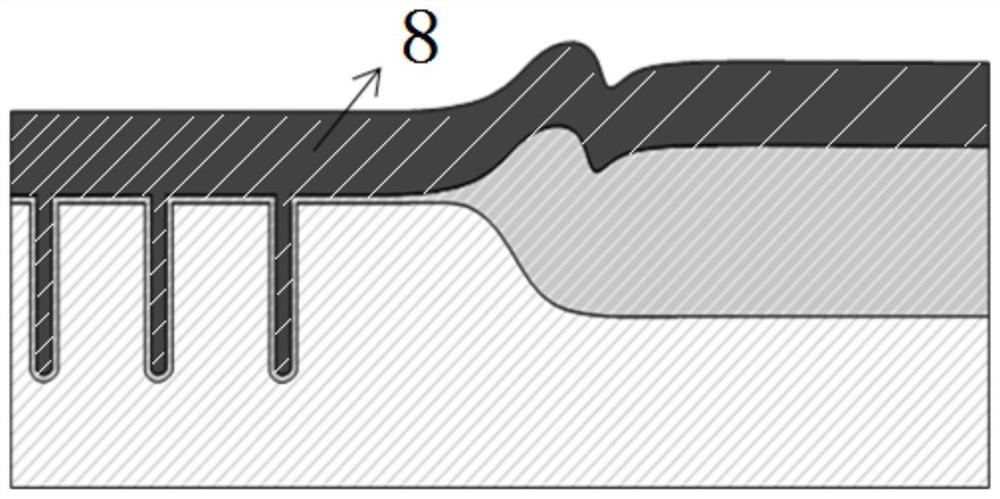

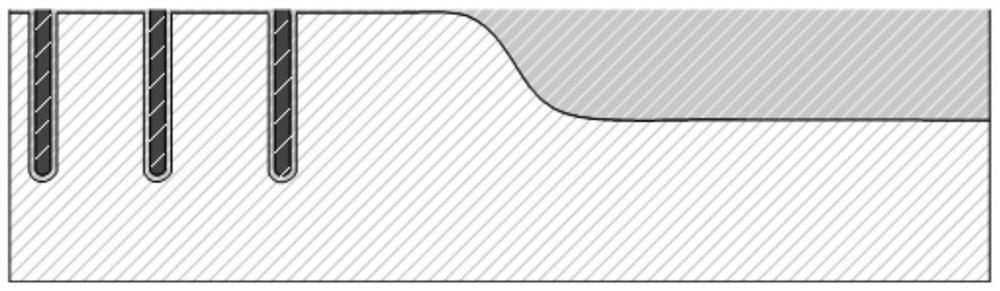

[0044] Step 5: If Figure 8 As shown, a hard mask layer is used as an etching barrier layer to form trenches 6 in the active region;

[0045] Step 6: If Figure 9 As shown, the damaged layer in the trench is removed by dry etching, and then gate oxide oxidation is performed after the damaged layer is removed to obtain the gate oxide layer 7 after the damaged layer i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More