Silicon carbide power semiconductor device testing method

A technology of power semiconductors and testing methods, which is applied in sorting and other directions, can solve the problems of a large number of gate oxide layer defects and limit commercial development, and achieve the effects of ensuring screening efficiency, improving factory yield, and improving screening accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

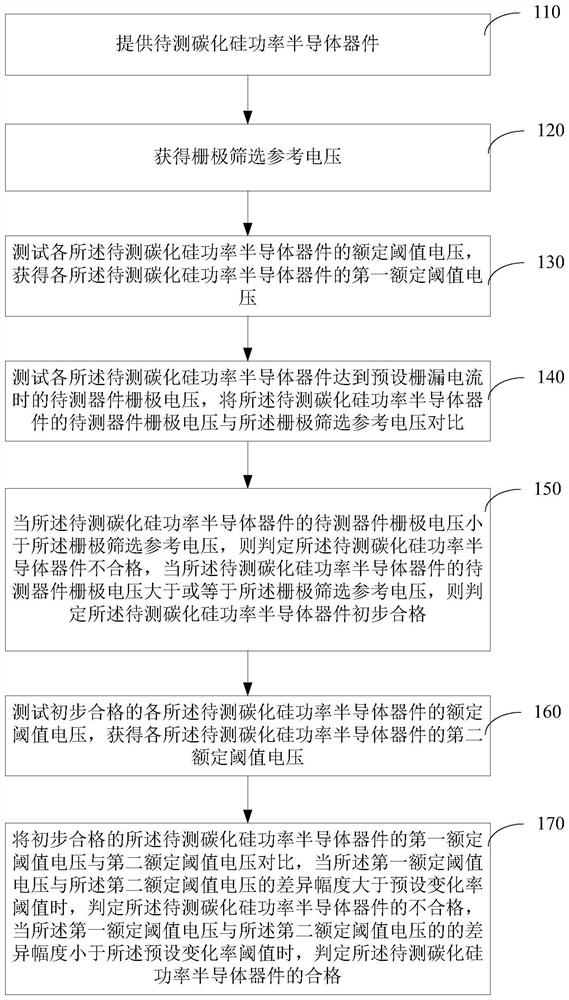

[0072] For better illustration, the detailed technical scheme of the present invention is as Figure 4 As shown, the details are as follows:

[0073] Step 1, conduct a preliminary test based on a certain number of target devices. The devices used for the preliminary test must meet the following requirements: include devices from different tape-out batches, and the tape-out batches must not be less than 3 batches; Devices from different wafers in the same tape-out batch; the number of devices from the same wafer shall not be less than 10.

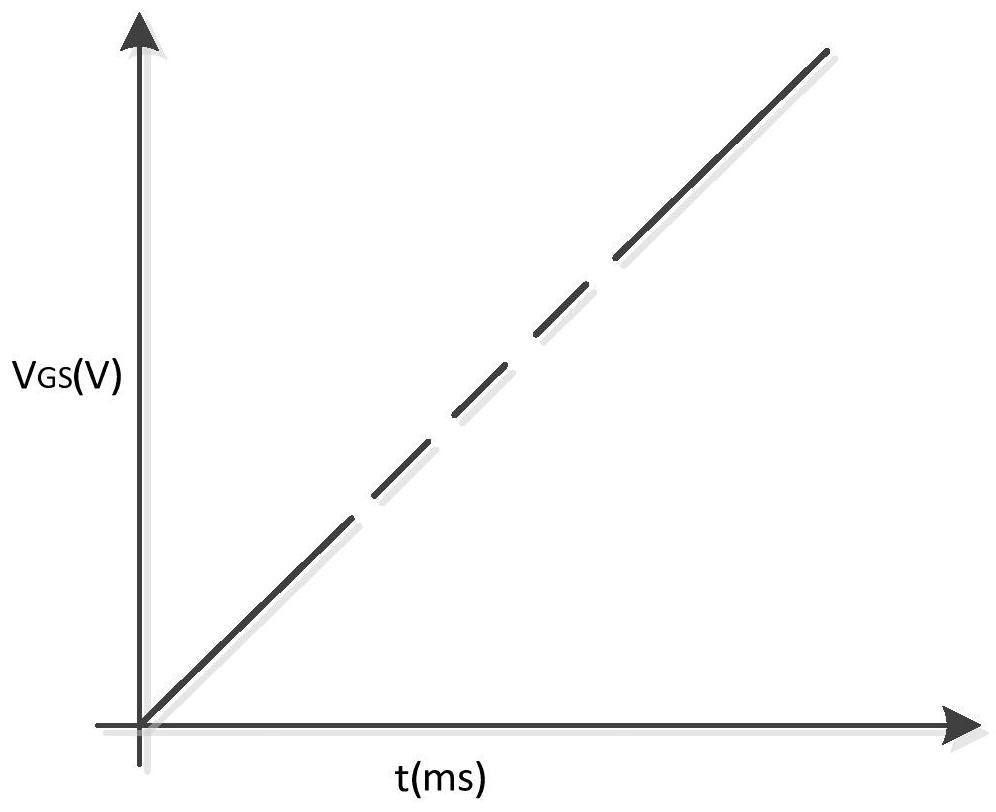

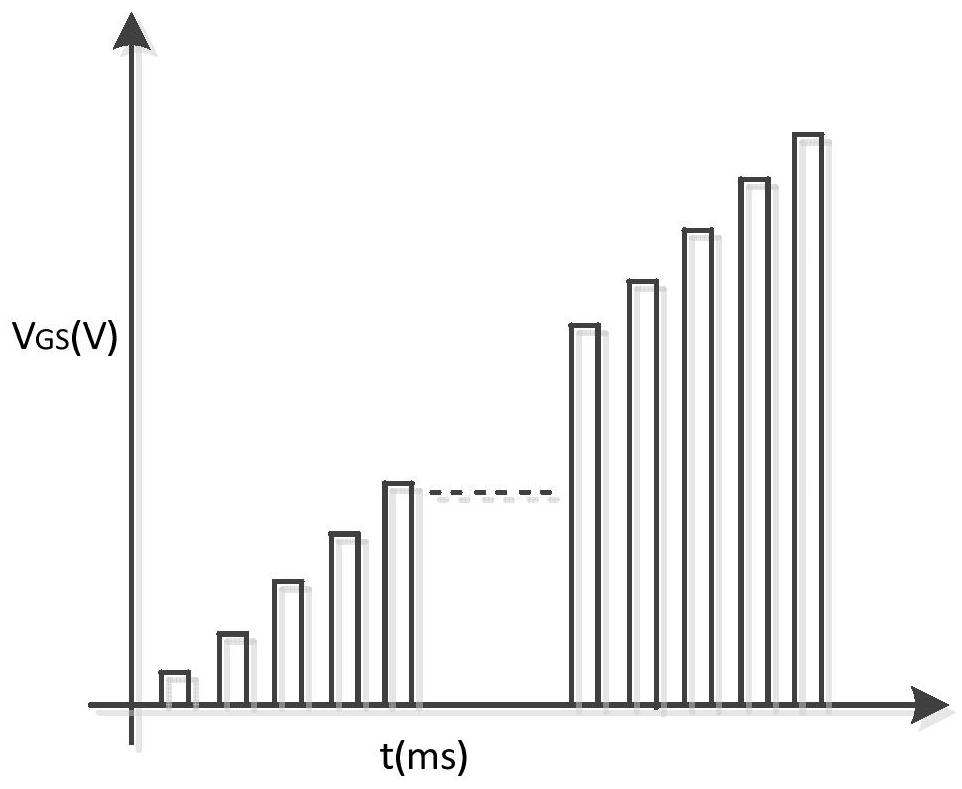

[0074] The bottom-up test is a gate-level leakage test, and the applied gate voltage signal is as follows: figure 2 or image 3 As shown, the test temperature is selected within the maximum allowable operating junction temperature or case temperature of the device. During the test, the gate voltage is continuously increased until the specific gate leakage current is reached, and the gate voltage under the specific gate leakage current is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com