N-surface GaN-based p-channel device for improving ohmic contact resistance and preparation method of N-surface GaN-based p-channel device

A technology of ohmic contact and channel devices, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problem of deteriorating the electrical characteristics of P-channel devices, reducing GaN hole mobility, and affecting the characteristics of P-channel devices and other problems, to increase the hole tunneling probability, reduce the barrier thickness, and improve the effect of ohmic contact characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

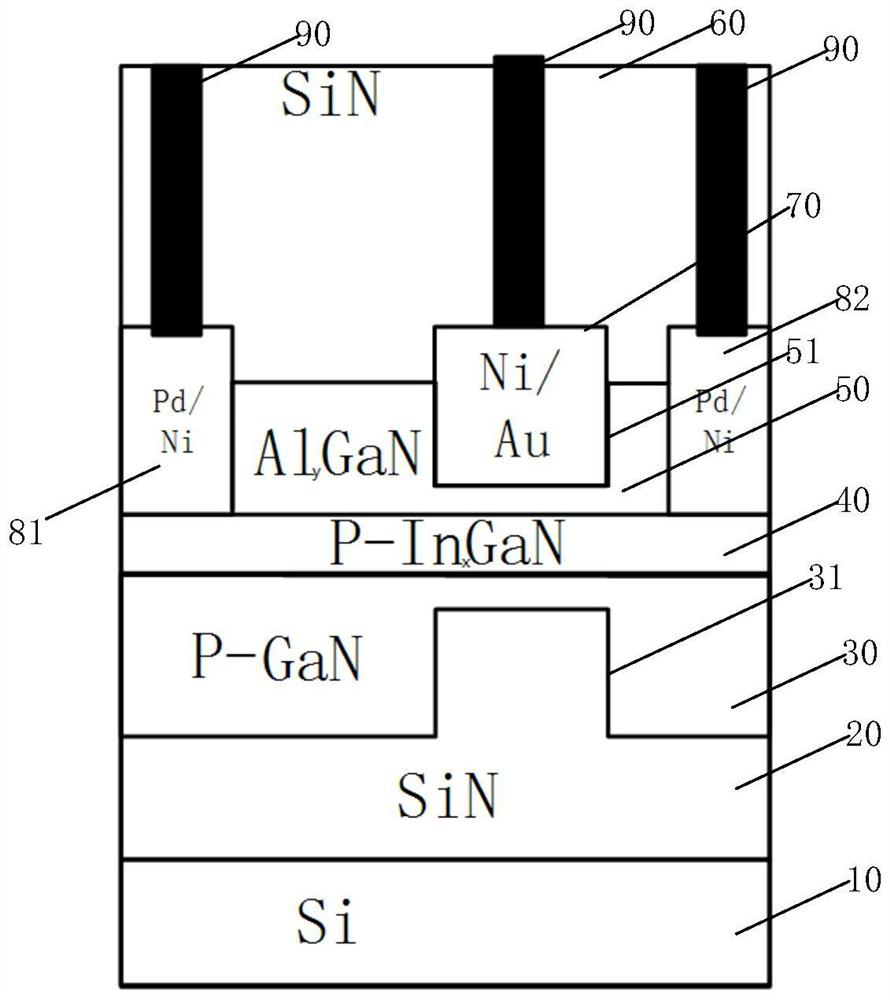

[0068] See figure 1 , an embodiment of the present invention provides an N-face GaN-based P-channel device with improved ohmic contact resistance, comprising: a first Si substrate layer 10, a first protective layer 20, a P-GaN layer 30, a P-GaN layer 30, a -In x GaN layer 40, Al y The GaN barrier layer 50 and the second protective layer 60 .

[0069] Al y GaN barrier layer 50, P-In x The GaN layer 40 and the P-GaN layer 30 form an N-plane heterojunction structure. A first groove 31 is formed on the P-GaN layer 30 . The notch of the first groove 31 faces the first protective layer 20 , and the first groove 31 is filled with the first protective layer 20 .

[0070] P-In x The Mg doping concentration of the GaN layer 40 is 2e19 / cm 3 ~3e19 / cm 3 , the thickness is 10nm ~ 20nm. Among them, 0.05≤x≤0.1.

[0071] Al y A second groove 51 opposite to the first groove 31 is formed on the GaN barrier layer 50 . Al y A source electrode 81 and a drain electrode 82 are deposited...

Embodiment 2

[0079] A second aspect of the embodiment of the present invention provides a method for preparing an N-face GaN-based P-channel device with improved ohmic contact resistance, which is used to prepare the device in the first embodiment, including the following steps:

[0080] Step 1. Epitaxially growing materials on the second Si substrate layer 11, the epitaxial layers are respectively the GaN buffer layer 12, the GaN layer 13, the Al from bottom to top y GaN barrier layer 50, P-In x GaN layer 40 and P-GaN layer 30; wherein, P-In x The Mg doping concentration of the GaN layer 40 is 2e19 / cm 3 ~3e19 / cm 3 , the thickness is 10nm ~ 20nm.

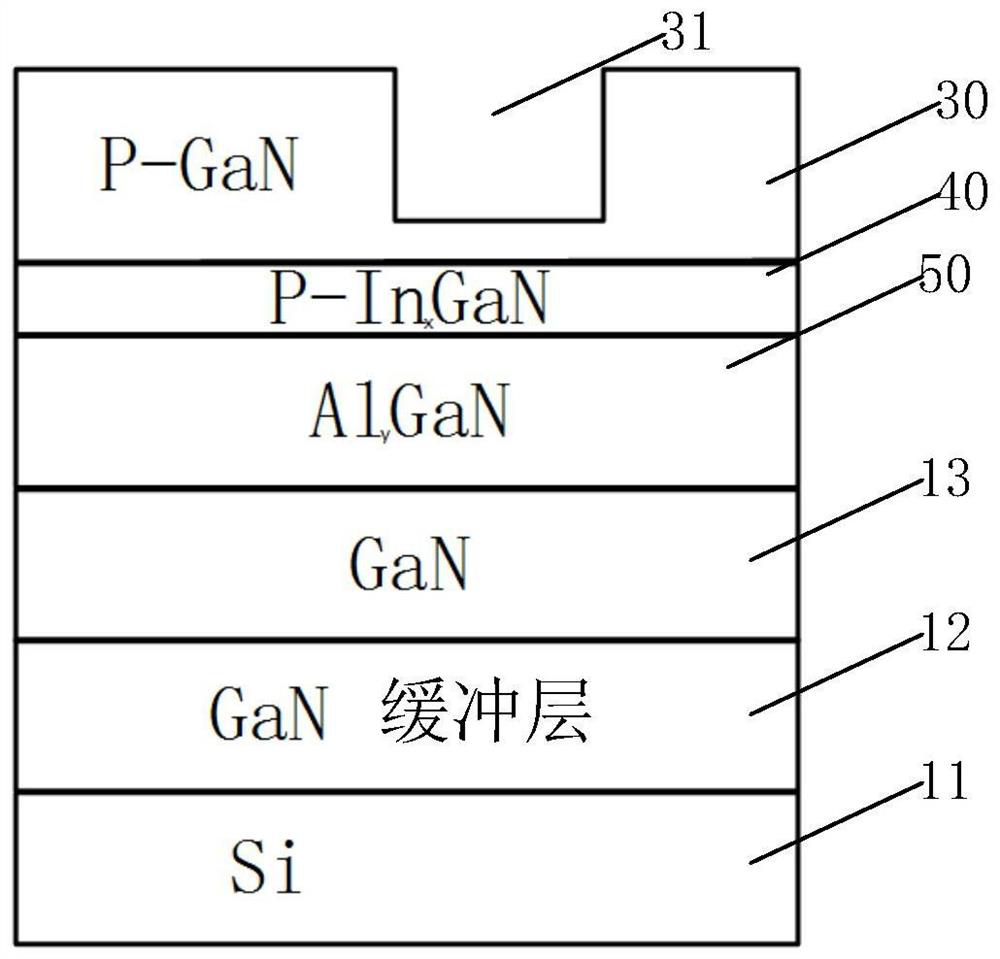

[0081] Step 2: Etching the first groove 31 on the P-GaN layer 30 .

[0082] Step 3, depositing the first protective layer 20 on the surface of the P-GaN layer 30 and filling the first groove 31 .

[0083] Step 4, bonding the first Si substrate layer 10 on the surface of the first protective layer 20 .

[0084] Step 5, turn over the product...

Embodiment 3

[0094] The embodiment of the present invention provides a method for preparing an N-face GaN-based P-channel device with improved ohmic contact resistance, which is used to prepare the device in the first embodiment, including the following steps:

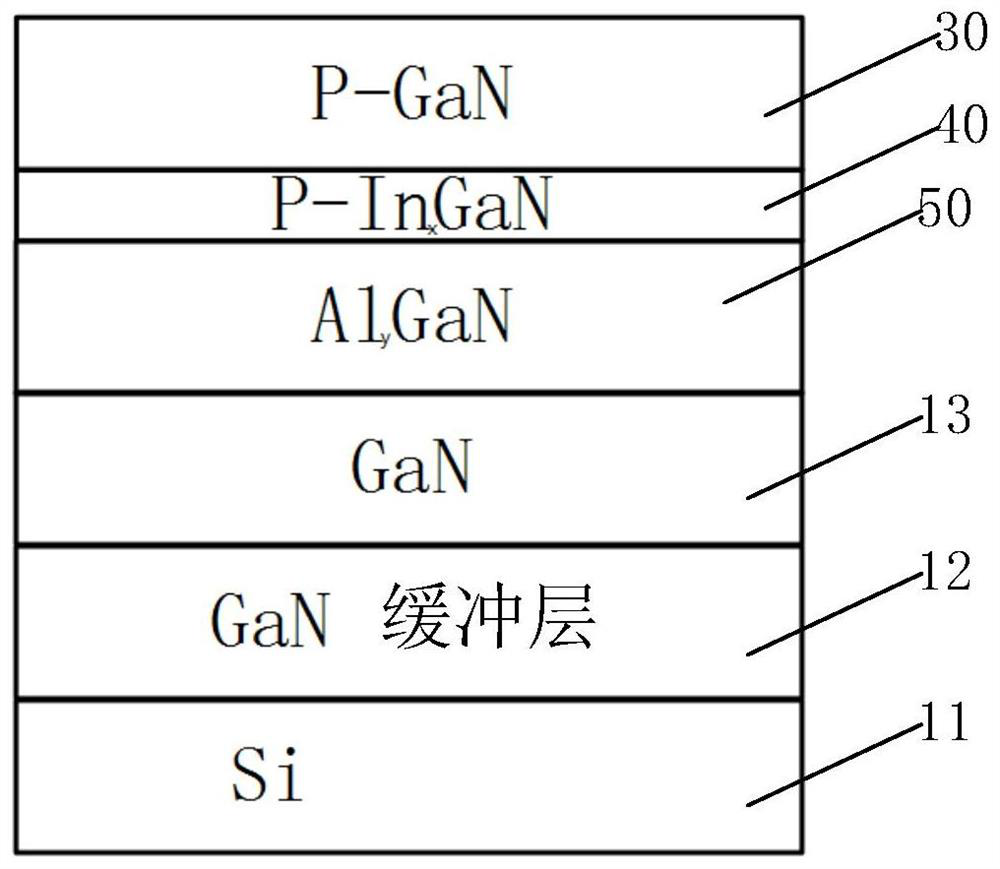

[0095] Step 301, using the MOCVD method to epitaxially grow the material on the second Si substrate layer 11, the epitaxial layers from bottom to top are the GaN buffer layer 12, the GaN layer 13, the Al y GaN barrier layer 50, P-In x GaN layer 40 and P-GaN layer 30; wherein, P-In x The Mg doping concentration of the GaN layer 40 is 2e19 / cm 3 ~3e19 / cm 3 , the thickness is 10nm ~ 20nm. like Figure 2a shown.

[0096] The thickness of the GaN buffer layer 12 is 2 μm to 5 μm. The thickness of the GaN layer 13 is 100 nm to 200 nm. Al y The thickness of the GaN barrier layer 50 is 15 nm to 25 nm. The thickness of the P-GaN layer 30 is 30 to 50 nm. The doping concentration of Mg in the P-GaN layer 30 is 2e19 / cm 3 ~3e19 / cm 3 ....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap