Copper interconnection layer and Damascus process method of copper interconnection layer

A process method, copper interconnection technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as poor results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

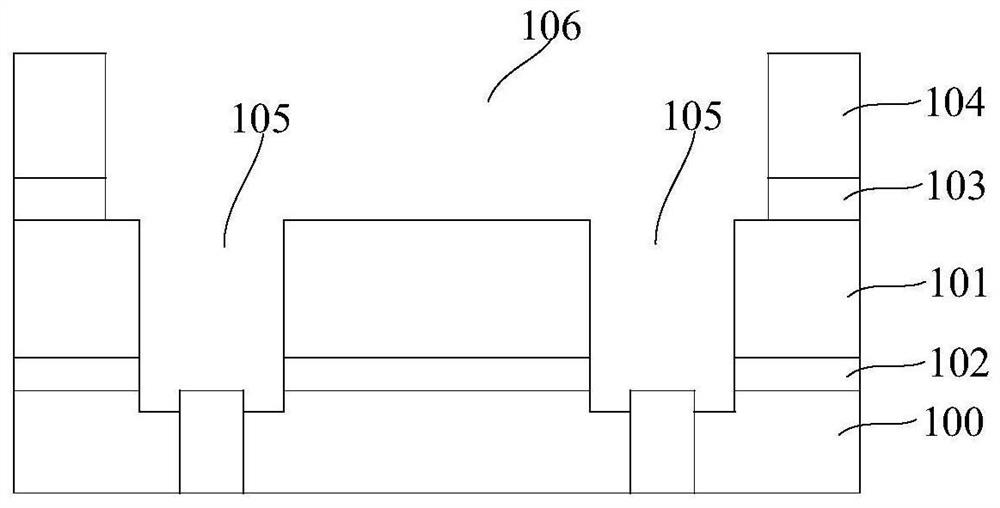

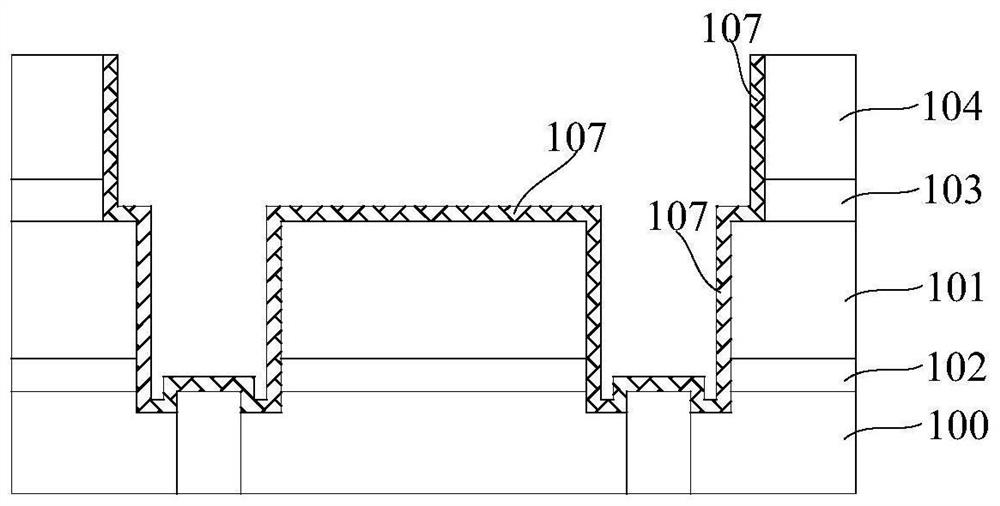

[0075] In the process of forming the copper interconnect layer by the Damascus process, such as Figure 14 As shown, the copper interconnect layer is formed in the dielectric layer 02 above the substrate 01, the dielectric layer is usually a low-k dielectric layer, and the copper 04 in the copper interconnect layer is easily migrated to the surrounding low-k dielectric layer or Diffusion, which in turn reduces the electron transport properties of copper. In order to prevent the migration or diffusion of copper to the dielectric layer, the barrier layer 03 is usually formed on the sidewall of the through hole or the trench where the interconnect layer is formed in the prior art. like Figure 14 As shown, taking a through hole as an example, a metal barrier layer 03 is formed on the sidewall and bottom of the through hole, and the barrier layer is usually Ta, TaN or Ta and TaN stack. In the conventional through interconnect layer, the above-mentioned metal barrier layer can ef...

Embodiment 2

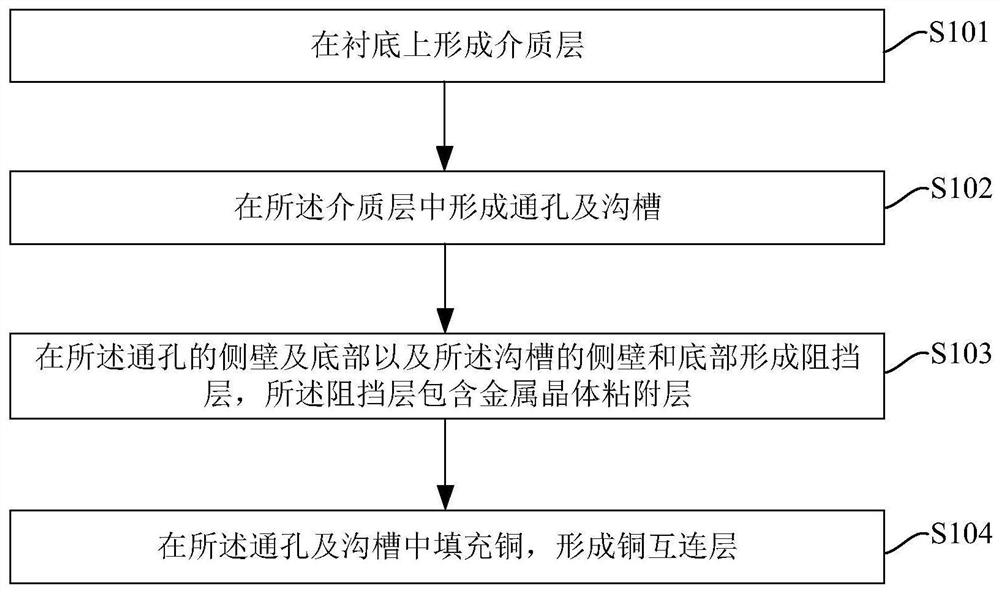

[0093] The present embodiment also provides a damascene process method for a copper interconnection layer, forming a barrier layer including a metal crystal adhesion layer on the sidewalls and bottoms of the through holes and trenches where the copper interconnection layer is formed, so as to effectively prevent copper from entering the surrounding dielectric. Layer migration and diffusion. like Figure 9 As shown, the method includes the following steps:

[0094] Step S201: forming a dielectric layer on the substrate;

[0095] Step S202: forming through holes and trenches in the dielectric layer;

[0096] Step S203: forming a barrier layer on the sidewall and bottom of the through hole and the sidewall and bottom of the trench, the barrier layer comprising a graphene layer; and

[0097] Step S204 : filling the through holes and trenches with copper to form a copper interconnection layer.

[0098] The above steps S201 , S202 and S204 are the same as the steps S101 , S102 a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More