Shield gate groove type field effect transistor with low on-resistance and preparation method thereof

A field effect transistor, low on-resistance technology, applied in the field of shielded gate trench type field effect transistor and its preparation, can solve the problem of high peak voltage, achieve the effect of improving switching speed and easy depletion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0052] In the SGT device, due to the electric field concentration effect and the high polysilicon doping concentration of the shielding gate, when the SGT device is blocked in the forward direction, the parasitic capacitance formed between the shielding gate and the substrate region is large, which reduces the switching speed of the transistor. .

[0053]Therefore, in order to improve the switching speed of the SGT device, the parasitic capacitance formed between the shielding gate and the substrate region needs to be weakened. Embodiments of the present application provide a shielded gate trench field effect transistor with low on-resistance.

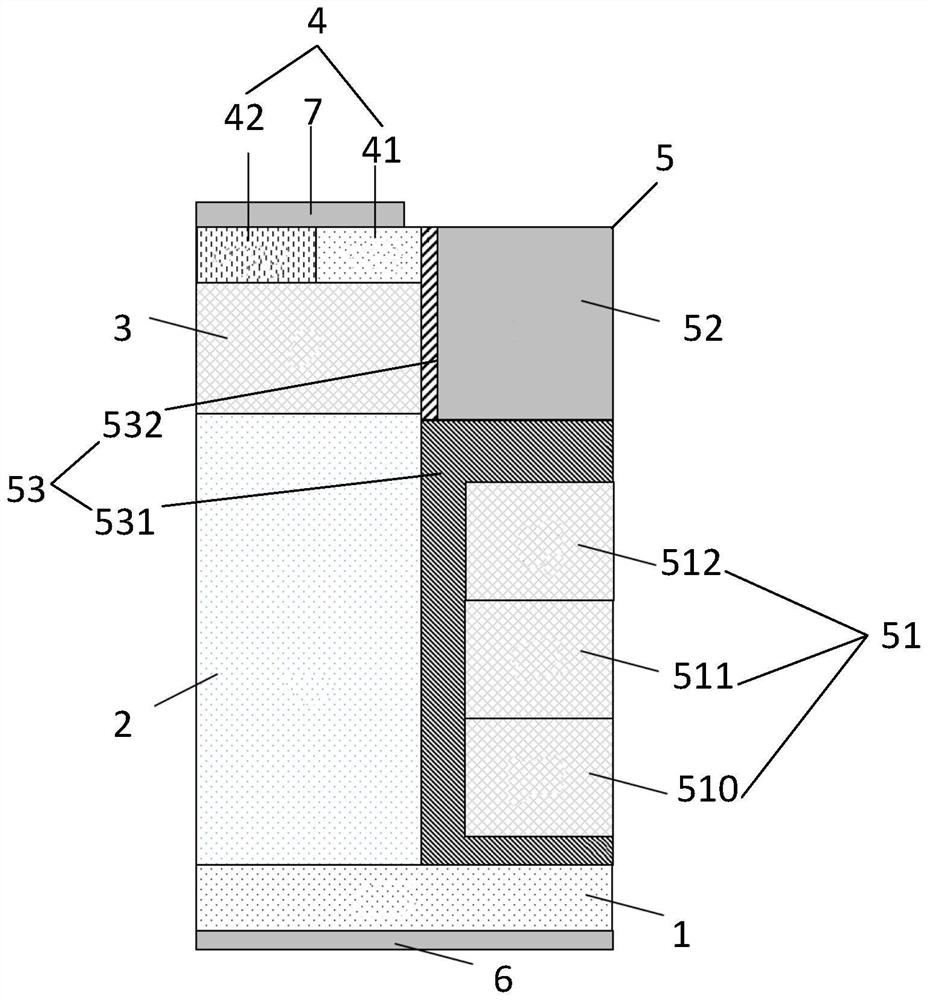

[0054] figure 1 It is a schematic structural diagram of the shielded gate trench field effect transistor with low on-resistance shown in the embodiment of the present application.

[0055] see figure 1 , the shielded gate trench field effect transistor with low on-resistance shown in the embodiment of the present application include...

Embodiment 2

[0070] Based on the transistor described in the first embodiment, due to the electric field concentration effect, when the SGT device is blocked in the forward direction, the electric charge and electric flux emitted by the ionization donor in the withstand voltage region are concentrated at the corner of the shield gate in the trench region, resulting in the channel The corners of the trench gates experience higher peak voltages.

[0071] Therefore, in order to improve the withstand voltage capability of the SGT device, it is necessary to weaken the electric field strength at the corners of the shield gate in the trench region. Embodiments of the present application provide a shielded gate trench field effect transistor with low on-resistance.

[0072] figure 1 It is a schematic structural diagram of the shielded gate trench field effect transistor with low on-resistance shown in the embodiment of the present application.

[0073] see figure 1 , the shielded gate trench fi...

Embodiment 3

[0087] Corresponding to the shielded-gate trench field effect transistor with low on-resistance shown in the first embodiment, the present application also provides a method for preparing a shielded-gate trench field-effect transistor with low on-resistance and the corresponding Example.

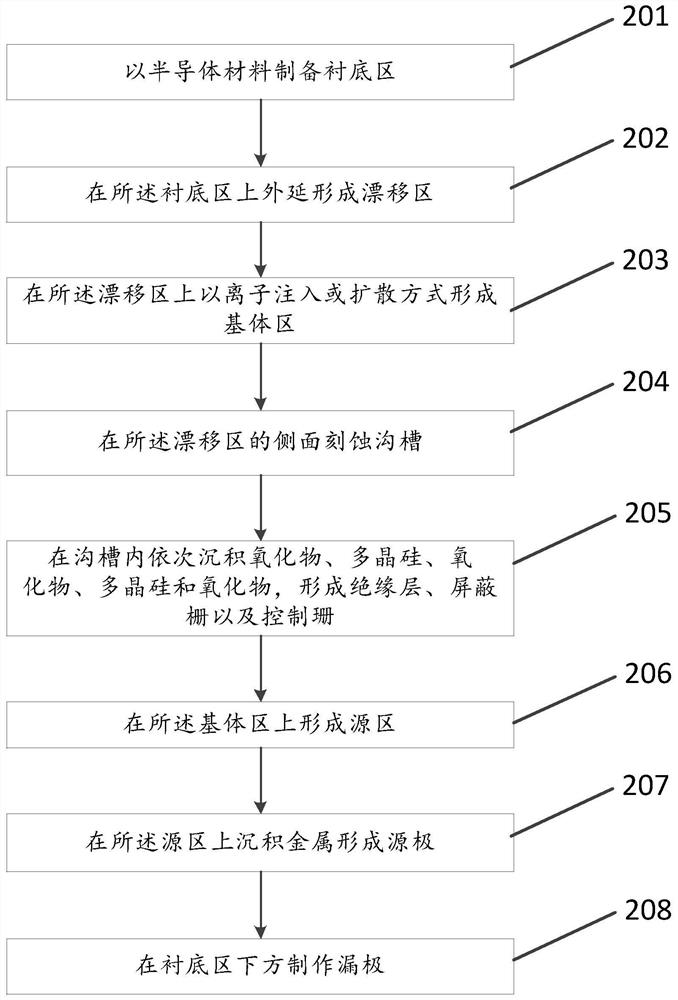

[0088] figure 2 It is a schematic flowchart of a method for fabricating a shielded gate trench field effect transistor according to an embodiment of the present application.

[0089] like figure 2 As shown, the method for fabricating the shielded gate trench field effect transistor with low on-resistance shown in the embodiment of the present application includes the following steps:

[0090] 201. Prepare a substrate region with a semiconductor material;

[0091] In the embodiment of the present application, the substrate region is prepared with N-type heavily doped semiconductor material, that is, the doping type of the substrate region is N-type doping, and the doping concentration of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com