Method for preparing self-aligning silicide of metal oxide semiconductor

A self-aligned silicide and oxide technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the complex preparation method, the unavoidable cobalt titanium cobalt silicide peak, junction leakage current and other problems. Problems such as breakdown voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

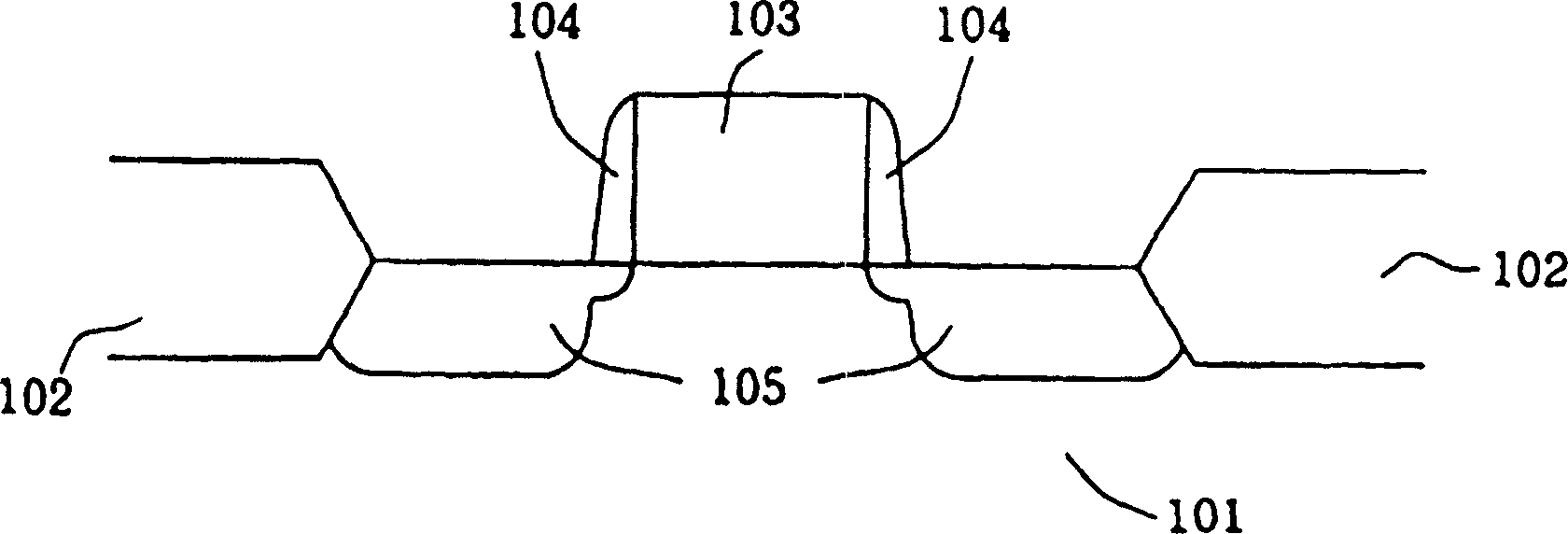

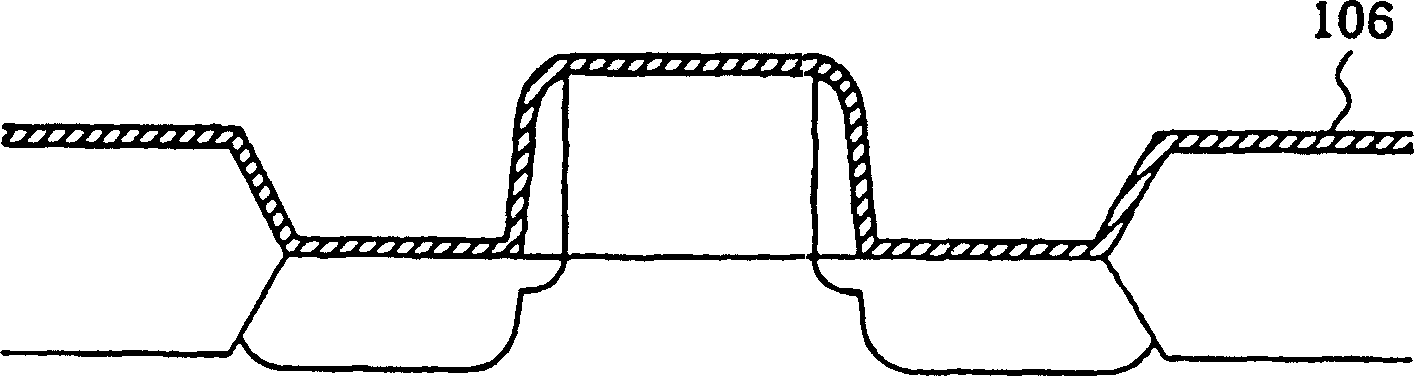

[0052] 2(a) to 2(e) are flow charts according to the first preferred embodiment of the present invention. First, a silicon substrate 201 is provided, the surface of the silicon substrate 201 has a gate 203, the lightly doped region 206 is located in the silicon substrate below the two sides of the gate 203, and the spacer 204 is located on the side of the gate 203 wall, and field oxide layer 202, as shown in Figure 2(a). Next, a heavy doping step is performed using the spacer 204 and the gate 203 as a mask, so that only the region below the spacer 204 remains in the lightly doped region 206, and the rest of the region forms the source / The drain region 205 is called a lightly doped drain (LDD) design, as shown in FIG. 2( b ).

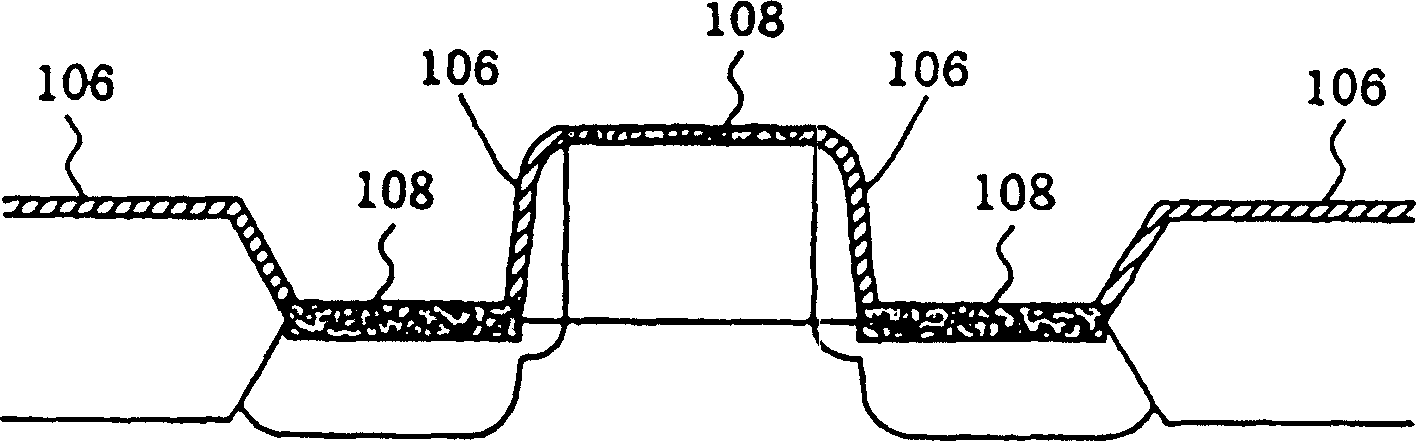

[0053] After that, a cobalt metal layer 207 is deposited on the surface of the field oxide layer 202, the source / drain region 205, the spacer 204 and the gate 203 by chemical deposition (CVD) or physical vapor deposition (PVD), such as Figure 2(c) sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More